Overview

CH390 is an industrial-grade Ethernet controller chip with its own 10/100M Ethernet Media Access Controller (MAC) and Physical Layer (PHY), supporting CAT3, 4, 5 for 10BASE-T and CAT5, 6 for 100BASE-TX connections, supporting HP Auto-MDIX, low-power consumption design, and complying with IEEE 802.3u specification. CH390 has built-in 16K bytes SRAM, supports 3.3V or 2.5V parallel interface and SPI serial interface for compatibility with various MCUs, MPUs, DSPs and other controllers.

Features

- It comes with its own internal Ethernet Media Access Controller (MAC) and Physical Layer (PHY)

- CH390L supports 8-bit and 16-bit parallel interface, CH390H supports SPI serial interface.

- Built-in unique Ethernet MAC address, no additional purchase or distribution, no external EEPROM.

- CH390H provides SPI slave interface and supports SPI clock modes 0 and 3 with clock speeds up to 50MHz.

- Integrated low-power 10/100M transceiver based on DSP algorithm implementation Transceiver.

- Support Auto-MDIX to exchange TX/RX and automatically identify positive and negative signal lines.

- Support 10BASE-T and 100BASE-TX and Auto-Negotiation.

- Support UTP CAT5E, CAT6 twisted pair cable, support 120 meters transmission distance.

- Support wake-up frames, link state changes, and magic packet events for remote wake-up.

- Support IEEE 802.3x flow control.

- Support IPv4 TCP/UDP and IPv6 TCP/UDP checksum generation and checking.

- Built-in LDO, support independent I/O interface power supply for different voltage processors or MCUs.

- Built-in 50Ω matching resistor, built-in crystal oscillator capacitor, and with lower BOM cost.

- Support optional external EEPROM configuration chip.

- Available in both QFN32 and LQFP48 packages.

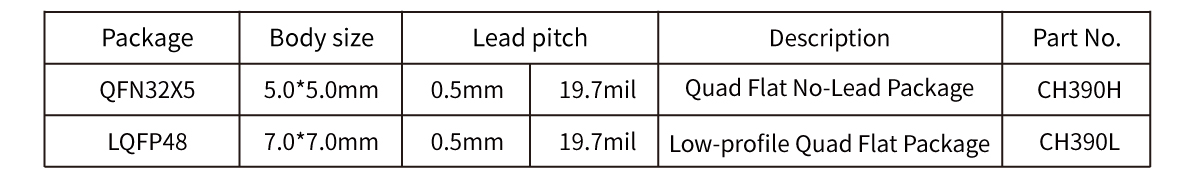

Package