# **USB-Host Interface Chip CH370**

Datasheet Version: 1B <u>http://wch.cn</u>

### 1. Overview

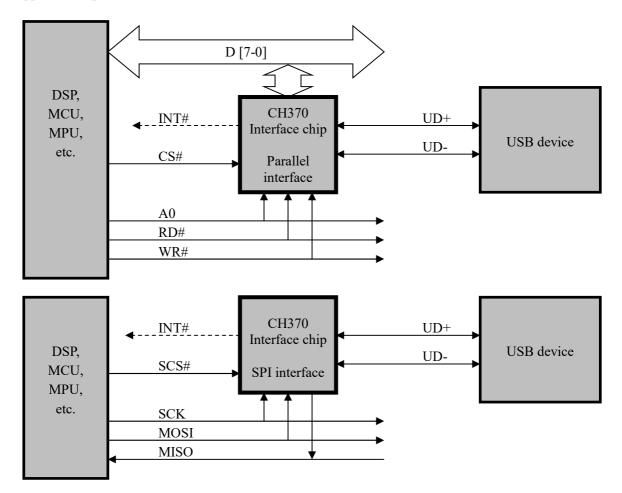

CH370 is a host interface chip of USB bus which supports low-speed and full-speed control transmission, bulk transmission and interrupt transmission. With the interface of controller such as DSP/MCU/MPU, it supports 8-bit parallel bus and 4-wire or 3-wire SPI serial bus.

### 2. Features

- Support 1.5Mbps low-speed and 12Mbps full-speed USB communication, compatible with USB V2.0.

- Support commonly used low-speed and full-speed USB device control transmission, bulk transmission and interrupt transmission.

- Automatically detect the connection and disconnection of USB device, and provide interrupt notifications for device connection and disconnection.

- Built-in impedance match series resistor of the USB signal line and the built-in pull-down resistor of the USB host terminal.

- Two MCU interfaces are optional: 8-bit passive parallel interface at the speed of 5MB and SPI serial interface at the speed of 3MB/24MHz.

- The SPI serial interface includes SPI chip selection, serial clock, serial input and output, and SPI output and input can be connected in parallel.

- The interrupt output pin is an optional connection and is active at low level. It can be replaced by querying the interrupt flag bit in the register.

- Support 5V supply voltage and 3.3V supply voltage, and having a function of built-in power-on reset. CH370V only supports 3.3V supply voltage.

- SSOP-20 lead-free package, and compatible with RoHS.

## 3. Package

| Package | Width o | f plastic | Pitch  | of pin | Instruction of<br>Package    | Ordering information |

|---------|---------|-----------|--------|--------|------------------------------|----------------------|

| SSOP-20 | 5.30mm  | 209mil    | 0.65mm | 25mil  | Subminiature 20-pin<br>patch | СН370Т               |

| SSOP-20 | 5.30mm  | 209mil    | 0.65mm | 25mil  | Subminiature 20-pin<br>patch | CH370V               |

Note: CH370V only supports 3.3V supply voltage, CH370T supports 5V supply voltage and 3.3V supply voltage.

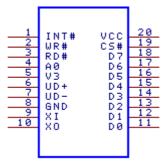

## 4. Pins

| Pin No. | Pin Name | Pin Type                     | Description                                                                                                                                                                                                                                                                               |

|---------|----------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

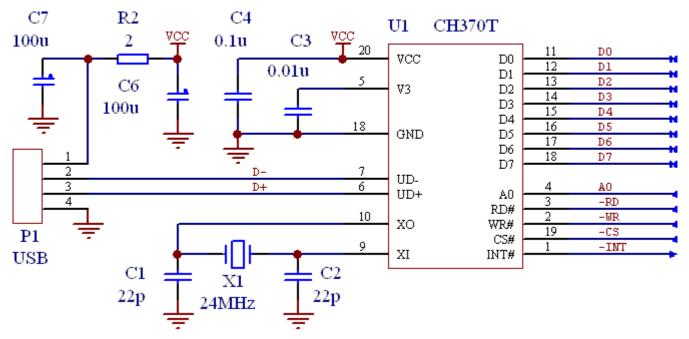

| 20      | VCC      | Power                        | Positive power input, an external 0.1uF power decoupling capacitor<br>is required                                                                                                                                                                                                         |

| 8       | GND      | Power                        | Common ground, required to be connected to the ground wire of<br>the USB bus                                                                                                                                                                                                              |

| 5       | V3       | Power                        | Connected to the VCC input external power source at the supply<br>voltage of 3.3V<br>Connected to an external 0.1uF decoupling capacitor at 5V supply<br>voltage                                                                                                                          |

| 9       | XI       | Input                        | Input terminal of the crystal oscillator, required to be connected to<br>an external crystal and oscillation capacitor                                                                                                                                                                    |

| 10      | XO       | Output                       | Inverted output terminal of the crystal oscillator, required to be<br>connected to an external crystal and oscillation capacitor                                                                                                                                                          |

| 6       | UD+      | USB signal                   | USB bus D+data line                                                                                                                                                                                                                                                                       |

| 7       | UD-      | USB signal                   | USB bus D - data cable                                                                                                                                                                                                                                                                    |

| 18~11   | D7~D0    | Bi-directional<br>Tri-status | <ul> <li>8-bit bidirectional data bus, built-in weak pull-up resistor</li> <li>D3 is also the SCS# of the SPI interface,</li> <li>D5 is also the SCK of the SPI interface,</li> <li>D6 is also the SDI of the SPI interface,</li> <li>D7 is also the SDO of the SPI interface.</li> </ul> |

| 3  | RD#  | Input                | Read strobe input, active low, built-in pull-up resistor                                 |

|----|------|----------------------|------------------------------------------------------------------------------------------|

| 2  | WR#  | Input                | Write strobe input, active low, built-in pull-up resistor                                |

| 19 | CS#  | Input                | Chip selection control input, active low, built-in weak pull-up resistor                 |

| 1  | INT# | Open-drain<br>output | Interrupt request output, active low, built-in pull-up resistor                          |

| 4  | A0   | Input                | Address line input, distinctive index port and data port, built-in weak pull-up resistor |

## 5. Register

The MCU referred to in this datasheet is basically applicable to DSP or SCM/MCU/MPU/CPU, etc.

The internal register and buffer area of CH370 are allocated in the address range from 00H to 0FFH, and are accessed after being addressed by the MCU.

The default value after reset is expressed in binary number, and its characteristics can be described by several character flags, which are as follows:

- 0: Always 0 after reset;

- 1: Always 1 after reset;

- X: This bit is automatically set by internal hardware or affected by the status of external pins;

- =: Reset does not affect the data, and the initial value of the data is uncertain;

- ?: Reserved bit; the read data has no meaning. You must write 0 or 1 or keep the original value when writing.

| Address<br>range<br>Hexadecimal<br>system | Register name (marked in<br>gray)<br>Bit name of register | Register description (marked in gray)<br>Bit description of the register                                                           | Default value<br>after software<br>/hardware reset |

|-------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 00H-03H                                   | Reserved Disable reading and writing                      |                                                                                                                                    | ????????                                           |

| 04H                                       | REG_SYS_INFO                                              | System information register, read only                                                                                             | XXX?XX01                                           |

| 04H bit 7                                 | BIT_INFO_POWER_RST                                        | Completion status of hardware power-on reset:<br>0=resetting; 1=reset completed                                                    | 0/X                                                |

| 04H bit6                                  | BIT_INFO_WAKE_UP                                          | The chip wake-up status is not affected by<br>software reset:<br>0=sleeping or waking up; 1=woken up                               | Х                                                  |

| 04H bit 5                                 | BIT_INFO_SOF_PRES                                         | LINFO_SOF_PRESHardware 1mS timing cycle status,<br>1= SOF packet will be generated                                                 |                                                    |

| 04H bit 4                                 | Reserved                                                  | The data read is meaningless and uncertain                                                                                         | ?                                                  |

| 04H bit 3                                 | BIT_INFO_USB_DP                                           | Logic level state of USB bus UD+ pin                                                                                               | Х                                                  |

| 04H bit 2                                 | BIT_INFO_USB_DM                                           | Logic level state of USB bus UD- pin                                                                                               | Х                                                  |

| 04H bit 1<br>04H bit 0                    | Hardware identification bit                               | Fixed value, always constant 01,<br>Used to verify that the hardware connection is<br>correct and the read operation is successful | 01                                                 |

| 05H                                       | REG_SYS_CTRL                                              | System control register, not affected by the software reset                                                                        | 00000000                                           |

| 05H bit 7<br>to 05H bit 4                 | It must be 0100                                           | The data read is meaningless and must be 0100                                                                                      | 0000                                               |

| 05H bit 3BIT_CRE_RESET_NOWChip solution feed control. 0-in reset [1-reset]005H bit 2BIT_CTRL_USB_POWERUSB power source regulator control of V3 pin:<br>0-Einable, generate USB power from 5V power<br>source of VCC pin;<br>1 = Disable; the USB power source can be<br>externally inputted from the V3 pin005H bit 1ReservedThe data read is meaningless and must be 0005H bit 2BIT_CTRL_OSCIL_OFF<br>0-coscillation allowed; 1-coscillation stopped<br>0-coscillation allowed; 1-coscillation stopped<br>0-coscilla                                                | 05111:4 2 | DIT CTDI DECET NOW | Chin astrono mast control. One accet 1-mast                                                                                                                                              | 0        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 05H bit 2BIT_CTRL_USB_POWER0=Enable, generate USB power from 5V power<br>source of VCC pin;<br>1 = Disable; the USB power source an be<br>externally inputted from the V3 pin005H bit 1ReservedThe data read is meaningless and must be 0005H bit 0BIT_CTRL_OSCIL_OFF<br>Oescillation allowed; 1=oscillation stopped000000006HREG_USB_SETUPUSB configuration register0000000006H bit 7It must be 1The data read is meaningless and must be 1006H bit 6BIT_SETP_AUTO_SOF<br>OFIsion-Automatically generate SOF enable;<br>0=Disable; 1=Enable; send out SOF packet<br>automatically0006H bit 5BIT_SETP_USB_SPEED-USB bus rate:<br>0=Disable; 1=Enable; send out SOF packet<br>automatically0006H bit 3BIT_SETP_USB_SPEED-USB bus rate:<br>0=Disable; 1=Enable; send out SOF packet<br>automatically0006H bit 3BIT_SETP_BUS_CTRL<br>00 or 1=disable the backup buffer;<br>1=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>10=disable; 1=table; develou:<br>10=disable; 1=table; develou:<br>10=disable;<br>11=UD-low UD-low (bus reset);<br>10=000006H bit 1BIT_SETP_BUS_CTRL<br>01=UD-low UD-low (bus reset);<br>10=01111000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 05H bit 3 | BIT_CTRL_RESET_NOW | Chip software reset control: 0=no reset; 1=reset                                                                                                                                         | 0        |

| 05H bit 0BIT_CTRL_OSCIL_OFFClock oscillator control:<br>$0-oscillation allowed; 1-oscillation stopped006HREG_USB_SETUPUSB configuration register000000006H bit 7It must be 1The data read is meaningless and must be 1006H bit 6BIT_SETP_AUTO_SOF0-Disable; 1=Enable, send out SOF packetautomatically generate SOF enable:0=Disable; 1=Enable, send out SOF packetautomatically006H bit 5BIT_SETP_USB_SPEED0-Disable; 1=Enable, send out SOF packetautomatically0006H bit 4BIT_SETP_USB_SPEED0-Disable; 1=Enable, send out SOF packetautomatically0006H bit 5BIT_SETP_RAM_MODEBackup buffer application method:00 \circ 01=disable the backup buffer;10=the second buffer are of continuous transmission,the synchronous flag is 1 and selected;11=the second buffer are of continuous transmission,the synchronous flag is 1 and selected;11=the second buffer are of continuous reception,the synchronous flag is 1 and selected;11=the second buffer area of continuous reception,the synchronous flag is 1 and selected;11=the second buffer area for continuous reception,the synchronous flag is 1 and selected;11=the second buffer area for continuous reception,the synchronous flag is 1 and selected;11=the second buffer area for continuous reception,the synchronous flag is 1 and selected;11=the second buffer area for continuous reception,the synchronous flag is 1 and selected;11=the second buffer area for continuous reception,the synchronous flag is 1 and selected;11=the second buffer area second $                                                                                                                                                                                                                                                                                                     | 05H bit 2 | BIT_CTRL_USB_POWER | 0=Enable, generate USB power from 5V power<br>source of VCC pin;<br>1= Disable; the USB power source can be                                                                              | 0        |

| 05H bit 0BIT_CTRL_OSCIL_OFFClock oscillator control:<br>$0=oscillation allowed; 1=oscillation stopped$ 006HREG_USB_SETUPUSB configuration register0000000006H bit 7It must be 1The data read is meaningless and must be 1006H bit 6BIT_SETP_AUTO_SOF0=Disable; 1=Enable, send out SOF packet<br>automatically generate SOF enable:<br>$0=Disable; 1=Enable, send out SOF packet$<br>automatically006H bit 5BIT_SETP_USB_SPEED00=12Mbps in full speed mode;<br>$0=12Mbps in full speed mode;$<br>$0=12Mbps in full speed mode;0=00006H bit 3BIT_SETP_RAM_MODEBackup buffer application method:00 \circ 0 = 1-disable the backup buffer;10=the second buffer are continuous transmission,the synchronous flag is 1 and selected;11=the second buffer are continuous transmission,the synchronous flag is 1 and selected;11=the second buffer are continuous transmission,the synchronous flag is 1 and selected;11=the second buffer are continuous transmission,the synchronous flag is 1 and selected;11=the second buffer are is0=0=0 mormal/idle;0=0=0 mormal/idle;0=0=0 mormal/idle;0=0=00006H bit 106H bit 0BIT_SETP_BUS_CTRLUSB bus status control:0=0=0 mormal/idle;0=0=0 mormal/idle;0=0=0 mormal/idle;0=0=0 mormal/idle;0=0=0 mormal/idle;0=0=0 mormal/idle;0=0=00007H bit 1to 07H bit 2Must be 111100The data read is meaningless and must be 111100111100007H bit 1to 07H bit 2BIT_E_TRANSFERUSB device datection interrupt enable:0=0 misabled; 1=enabled, output from INT# pin0=0007H bit 1<$                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 05H bit 1 | Reserved           |                                                                                                                                                                                          | 0        |

| $06H$ bit 7It must be 1The data read is meaningless and must be 10 $06H$ bit 6BIT_SETP_AUTO_SOF $0$ =Disable; 1=Enable, send out SOF packet<br>automatically generate SOF enable:<br>$0$ =Disable; 1=Enable, send out SOF packet<br>automatically0 $06H$ bit 5BIT_SETP_USB_SPEED $00$ =12Mbps in full speed mode;<br>$11=1.5Mbps in low speed mode;00 \circ 0^{1}=disabled0006H bit 4BIT_SETP_USB_SPEED00=12Mbps in low speed mode;00 \circ 0^{1}=disabled0006H bit 306H bit 2BIT_SETP_RAM_MODEBackup buffer application method:00 \circ 0^{1}=disable the backup buffer;10=the second buffer of continuous transmission,the synchronous flag is 1 and selected;11=the second buffer area of continuous reception.10=disabled;11=UD+low UD-low (bus reset);10=disabled;11=UD+low UD-low (bus recevery)0006H bit 106H bit 0BIT_SETP_BUS_CTRL00=normal/idle;00=normal/idle;11=UD+low UD-low (bus recevery)0007H Mto 07H bit 7to 07H bit 1Must be 111100The data read is meaningless and must be 111100111100007H bit 0BIT_IE_DEV_DETECTUSB device detection interrupt enable:0=disabled; 1=enabled, output from INT# pin0=disabled; 1=enabled, output from INT# pin007H bit 0BIT_BE_ADDRUSB device address register0000000008H bit 608H REG_USB_ADDRUSB device currently being operated0000000008H bit 608H bit0BIT_ADDR_USB_DEVAddress of USB device currently being operated0000000009H bit 7BIT_IF_USB_DX_INAddress of USB device detec$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 05H bit 0 | BIT_CTRL_OSCIL_OFF | Clock oscillator control:                                                                                                                                                                | 0        |

| Of H bit 6BIT_SETP_AUTO_SOFAutomatically generate SOF enable:<br>0=Disable; 1=Enable, send out SOF packet<br>automatically006H bit 5<br>06H bit 4BIT_SETP_USB_SPEEDUSB bus rate:<br>00=12Mbps in full speed mode;<br>01=15Mbps in low speed mode;<br>0H bit 40006H bit 5<br>06H bit 4BIT_SETP_USB_SPEED00=12Mbps in full speed mode;<br>00 of 1=2Mbps in low speed mode;<br>00 or 01=disable the backup buffer;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>10=disabled;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;0006H bit 1<br>06H bit 0BIT_SETP_BUS_CTRL01=UD+low UD-low (bus reset);<br>10=disabled;<br>11=UD+low UD-ligh (bus recovery)0007H bit 7<br>to 07H bit 7Must be 111100The data read is meaningless and must be 111100111100007H bit 1<br>bit 7<br>to 7H bit 1BIT_IE_TRANSFERUSB device detection interrupt enable:<br>0=disabled; 1=enabled, output from INT# pin008H<br>bit 6<br>to 08H bit 7REG_USB_ADDRUSB device currently being operated0000000008H bit 7<br>09H bit 7BIT_ADDR_USB_DEVAd                                                                                                                                                                                                                                              | 06H       | REG_USB_SETUP      | USB configuration register                                                                                                                                                               | 0000000  |

| 06H bit 6<br>0<br>06H bit 7<br>06H bit 1<br>06H bit 1<br>06H bit 3BIT_SETP_USB_SPED<br>BIT_SETP_USB_SPED0=Disable; 1=Enable, send out SOF packet<br>automatically<br>06=12Mbps in full speed mode;<br>06H bit 4006H bit 5<br>06H bit 4BIT_SETP_USB_SPED00=12Mbps in full speed mode;<br>00=12Mbps in low speed mode;<br>Other value = disabled0006H bit 3<br>06H bit 2BIT_SETP_RAM_MODEBackup buffer application method:<br>00 or o1=disable the backup buffer;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer;<br>10=the second buffer;<br>10=disabled;<br>11=UD+low UD-low (bus reset);<br>10=disabled;<br>11=UD+low UD-low (bus recovery)0006H bit 1<br>06H bit 0BIT_SETP_BUS_CTRLUSB device detection interrupt enable:<br>0=disabled;<br>11=UD+low UD-ling (bus recovery)0007H bit 1<br>07H bit 2Must be 111100The data read is meaningless and must be 1111001111000007H bit 1<br>07H bit 1BIT_IE_DEV_DETECTUSB device detection interrupt enable:<br>0=disabled; 1=enabled, output from INT# pin<br>0=disabled; 1=enabled, output from INT# pin008H<br>08H<br>08HREG_USB_ADDRUSB device address register0000000008H bit 7ReservedThe data read is meaningless and must be 0008H bit 7<br>08H bit 7BIT_ADDR_USB_DEVAddress of USB device admess register0000000009H bit 7BIT_IF_USB_DX_INSample status of UD+ pin at full speed/UD- pin at <br< td=""><td>06H bit 7</td><td>It must be 1</td><td>The data read is meaningless and must be 1</td><td>0</td></br<>                                                                                                                                                                                                                     | 06H bit 7 | It must be 1       | The data read is meaningless and must be 1                                                                                                                                               | 0        |

| 06H bit 5<br>06H bit 4BIT_SETP_USB_SPEED00=12Mbps in full speed mode:<br>11=1.5Mbps in low speed mode;<br>Other value = disabled0006H bit 3<br>06H bit 2Barsand speed mode:<br>00 or 01=disable the backup buffer application method:<br>00 or 01=disable the backup buffer;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>10=the second buffer of continuous transmission,<br>one<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer of continuous transmission,<br>0006H bit 1<br>to 07H bit 7<br>to 07H bit 7BIT_EE_TEANSFERUSB device detection interrupt enable:<br>0=disabled; 1=enabled, output from INT# pin<br>0=disabled; 1=enabled, output from INT | 06H bit 6 | BIT_SETP_AUTO_SOF  | 0=Disable; 1=Enable, send out SOF packet                                                                                                                                                 | 0        |

| 06H bit 3<br>06H bit 2BIT_SETP_RAM_MODE00 or 01=disable the backup buffer;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>10=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception,<br>the synchronous flag is 1 and selected;<br>11=the-flag tegister00007HREG_INTER_ENInterrupt enable register1111000007H bit 7<br>to 07H bit 2Must be 11110011110011110007H bit 0BIT_IE_TRANSFERUSB device detection interrupt enable:<br>0=disabled; 1=enabled, output from INT# pin<br>0=disabled; 1=enabled, output from INT# pin<br>0=disabled; 1=enabled, output from INT# pin<br>0008H bit 7Reeg_USB_ADDRUSB device address register0000000008H bit 7Reeg_USB_ADDRAddress of USB device currently being operated<br>10 ws peedi:<br>0=low level/speed mismatch;<br>1=high                                                                                                                                                  |           | BIT_SETP_USB_SPEED | 00=12Mbps in full speed mode;<br>11=1.5Mbps in low speed mode;                                                                                                                           | 00       |

| 06H bit 1<br>06H bit 0BIT_SETP_BUS_CTRL00=normal/idle;<br>01=UD+low UD-low (bus reset);<br>10=disabled;<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | BIT_SETP_RAM_MODE  | 00 or 01=disable the backup buffer;<br>10=the second buffer of continuous transmission,<br>the synchronous flag is 1 and selected;<br>11=the second buffer area of continuous reception, | 00       |

| 07H bit 7<br>to 07H bit 2Must be 111100The data read is meaningless and must be 11110011110007H bit 2Must be 111100The data read is meaningless and must be 11110011110007H bit 1BIT_IE_DEV_DETECTUSB device detection interrupt enable:<br>0=disabled; 1=enabled, output from INT# pin007H bit 0BIT_IE_TRANSFERUSB transmission completion interrupt enable:<br>0=disabled; 1=enabled, output from INT# pin008HREG_USB_ADDRUSB device address register0000000008H bit 7ReservedThe data read is meaningless and must be 0008H bit6<br>to 08H bit0BIT_ADDR_USB_DEVAddress of USB device currently being operated<br>0000000000000009HREG_INTER_FLAGInterrupt flag register, read onlyX0X0000009H bit 7BIT_IF_USB_DX_INSample status of UD+ pin at full speed/UD- pin at<br>low speed:<br>0=low level/speed mismatch;<br>1=high level/speed matchX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | BIT_SETP_BUS_CTRL  | 00=normal/idle;<br>01=UD+low UD-low (bus reset);<br>10=disabled;                                                                                                                         | 00       |

| to 07H bit 2Must be 111100The data read is meaningless and must be 11110011110007H bit 1BIT_IE_DEV_DETECTUSB device detection interrupt enable:<br>0=disabled; 1=enabled, output from INT# pin007H bit 0BIT_IE_TRANSFERUSB transmission completion interrupt enable:<br>0=disabled; 1=enabled, output from INT# pin008HREG_USB_ADDRUSB device address register0000000008H bit 7ReservedThe data read is meaningless and must be 0008H bit6<br>to 08H bit0BIT_ADDR_USB_DEVAddress of USB device currently being operated<br>09H000000009HREG_INTER_FLAGInterrupt flag register, read onlyX0X0000009H bit 7BIT_IF_USB_DX_INSample status of UD+ pin at full speed/UD- pin at<br>low speed:<br>0=low level/speed mismatch;<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 07H       | REG_INTER_EN       | Interrupt enable register                                                                                                                                                                | 11110000 |

| 0/H bit 1BIT_IE_DEV_DETECT0=disabled; 1=enabled, output from INT# pin007H bit 0BIT_IE_TRANSFERUSB transmission completion interrupt enable:<br>0=disabled; 1=enabled, output from INT# pin008HREG_USB_ADDRUSB device address register0000000008H bit 7ReservedThe data read is meaningless and must be 0008H bit6<br>to 08H bit0BIT_ADDR_USB_DEVAddress of USB device currently being operated000000009HREG_INTER_FLAGInterrupt flag register, read onlyX0X0000009H bit 7BIT_IF_USB_DX_INSample status of UD+ pin at full speed/UD- pin at<br>low speed:<br>1=high level/speed mismatch;<br>1=high level/speed matchX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | Must be 111100     | The data read is meaningless and must be 111100                                                                                                                                          | 111100   |

| 0/H bit 0BIT_IE_TRANSFER0=disabled; 1=enabled, output from INT# pin008HREG_USB_ADDRUSB device address register0000000008H bit 7ReservedThe data read is meaningless and must be 0008H bit6<br>to 08H bit0BIT_ADDR_USB_DEVAddress of USB device currently being operated000000009HREG_INTER_FLAGInterrupt flag register, read onlyX0X0000009H bit 7BIT_IF_USB_DX_INSample status of UD+ pin at full speed/UD- pin at<br>low speed:<br>1=high level/speed mismatch;<br>1=high level/speed matchX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 07H bit 1 | BIT_IE_DEV_DETECT  | -                                                                                                                                                                                        | 0        |

| 08H bit 7ReservedThe data read is meaningless and must be 0008H bit6<br>to 08H bit0BIT_ADDR_USB_DEV<br>BIT_ADDR_USB_DEVAddress of USB device currently being operated<br>Address of USB device currently being operated000000009HREG_INTER_FLAGInterrupt flag register, read onlyX0X0000009H bit 7BIT_IF_USB_DX_INSample status of UD+ pin at full speed/UD- pin at<br>low speed:<br>1=high level/speed mismatch;<br>1=high level/speed matchX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 07H bit 0 | BIT_IE_TRANSFER    | · ·                                                                                                                                                                                      | 0        |

| 08H bit 7ReservedThe data read is meaningless and must be 0008H bit6<br>to 08H bit0BIT_ADDR_USB_DEV<br>BIT_ADDR_USB_DEVAddress of USB device currently being operated<br>Address of USB device currently being operated000000009HREG_INTER_FLAGInterrupt flag register, read onlyX0X0000009H bit 7BIT_IF_USB_DX_INSample status of UD+ pin at full speed/UD- pin at<br>low speed:<br>1=high level/speed mismatch;<br>1=high level/speed matchX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 08H       | REG_USB_ADDR       | USB device address register                                                                                                                                                              | 00000000 |

| 08H bit6<br>to 08H bit0BIT_ADDR_USB_DEVAddress of USB device currently being operated000000009HREG_INTER_FLAGInterrupt flag register, read onlyX0X0000009H bit 7BIT_IF_USB_DX_INSample status of UD+ pin at full speed/UD- pin at<br>low speed:<br>1=high level/speed mismatch;<br>1=high level/speed matchX0X00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 08H bit 7 | Reserved           | The data read is meaningless and must be 0                                                                                                                                               | 0        |

| 09H bit 7     BIT_IF_USB_DX_IN     Sample status of UD+ pin at full speed/UD- pin at low speed:       0=low level/speed mismatch;     1=high level/speed match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | BIT_ADDR_USB_DEV   |                                                                                                                                                                                          | 0000000  |

| 09H bit 7     BIT_IF_USB_DX_IN     low speed:<br>0=low level/speed mismatch;<br>1=high level/speed match     X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 09H       | REG_INTER_FLAG     | Interrupt flag register, read only                                                                                                                                                       | X0X00000 |

| 09H bit 6ReservedThe data read is meaningless0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 09H bit 7 | BIT_IF_USB_DX_IN   | low speed:<br>0=low level/speed mismatch;<br>1=high level/speed match                                                                                                                    | Х        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 09H bit 6 | Reserved           | The data read is meaningless                                                                                                                                                             | 0        |

#### http://wch.cn

|                           |                                                                                                                                                                                                              | Current connection status of UCD devices                                                                                                                                                                                                                                                                                                                                                                                        | <b>I</b> |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| 09H bit 5                 | BIT_IF_DEV_ATTACH                                                                                                                                                                                            | Current connection status of USB device:<br>0= no USB device is connected/ disconnected/<br>unplugged;<br>1= at least one USB device has been connected/<br>plugged in                                                                                                                                                                                                                                                          | =/X      |  |  |

| 09H bit 4                 | BIT_IF_USB_PAUSE                                                                                                                                                                                             | USB transmission pause flag,<br>Effective in case of 1; write 1 to this bit to clear,<br>This bit is automatically set to 1 after each USB<br>transfer is completed                                                                                                                                                                                                                                                             | 0/X      |  |  |

| 09H bit 3                 | BIT_IF_WAKE_UP                                                                                                                                                                                               | BIT_IF_WAKE_UP Chip wake-up completion interrupt flag,<br>Effective in case of 1; write 1 to this bit to clear,<br>This bit is automatically set to 1 after the chip<br>wake-up is completed                                                                                                                                                                                                                                    |          |  |  |

| 09H bit 2                 | Reserved                                                                                                                                                                                                     | The data read is meaningless                                                                                                                                                                                                                                                                                                                                                                                                    | 0/X      |  |  |

| 09H bit 1                 | BIT_IF_DEV_DETECT                                                                                                                                                                                            | USB device plug detection interrupt flag,<br>Effective in case of 1; write 1 to this bit to clear,<br>This bit is automatically set to 1 after detecting<br>that the USB device is plugged or unplugged                                                                                                                                                                                                                         | 0/X      |  |  |

| 09H bit 0                 | 09H bit 0 BIT_IF_TRANSFER USB transmission completion interrupt flag,<br>Effective in case of 1; write 1 to this bit to clear,<br>This bit is automatically set to 1 after each USB<br>transfer is completed |                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0/X      |  |  |

| 0AH                       | REG_USB_STATUS       USB status register, read only,         Usually only querying after the corresponding interrupt is detected                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1XXXXXXX |  |  |

| 0AH bit 7                 | BIT_STAT_SIE_FREE                                                                                                                                                                                            | Status of current USB interface engine SIE:<br>0=busy/transmitting; 1=idle/waiting                                                                                                                                                                                                                                                                                                                                              | 1/X      |  |  |

| 0AH bit 6                 | Reserved                                                                                                                                                                                                     | The data read is meaningless                                                                                                                                                                                                                                                                                                                                                                                                    | Х        |  |  |

| 0AH bit 5                 | Reserved                                                                                                                                                                                                     | The data read is meaningless                                                                                                                                                                                                                                                                                                                                                                                                    | Х        |  |  |

| 0AH bit 4                 | BIT_STAT_TOG_MATCH                                                                                                                                                                                           | Indicate whether the current USB transmission is<br>successful:<br>0= transmission failure;<br>1= transmission success and synchronization                                                                                                                                                                                                                                                                                      | Х        |  |  |

| 0AH bit 3<br>to 0AH bit 0 | BIT_STAT_DEV_RESP                                                                                                                                                                                            | Reply PID of USB device:<br>0010= transaction reply ACK of device for<br>OUT/SETUP;<br>1010= transaction reply NAK of device for<br>IN/OUT/SETUP;<br>1110= transaction reply STALL of device for<br>IN/OUT/SETUP;<br>0011= transaction reply DATA0 of device for IN<br>1011= transaction reply DATA1 of device for IN<br>XX00=device reply error or no reply in case of<br>timeout;<br>Other values = illegal response/accident | XXXX     |  |  |

| 0BH                       | REG_USB_LENGTH                                                                                                                                                                                               | USB length register, read only/write only,<br>Read the receive length of the USB host,                                                                                                                                                                                                                                                                                                                                          | XXXXXXXX |  |  |

|                           |                    | Write the transmit length of the USB host,                                                                                                                                                                                                                 |          |

|---------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0CH                       | Reserved           | Disable reading and writing                                                                                                                                                                                                                                | ???????? |

| 0DH                       | REG_USB_H_TOKEN    | USB host token register                                                                                                                                                                                                                                    |          |

| 0DH bit 7<br>to 0DH bit 4 | BIT_HOST_PID_TOKEN | Specify transaction/token PID:<br>1101=SETUP transaction; 0001=OUT transaction;<br>1001=IN transaction; 0101=SOF packet; other<br>values=disabled.<br>Note: After the SOF packet is completed, there is<br>no interrupt, and the SIE status can be queried |          |

| 0DH bit 3<br>to 0DH bit 0 | BIT_HOST_PID_ENDP  | Specify the number of destination terminal to be<br>operated:<br>0000 to 1111=terminal number 0 to 15                                                                                                                                                      |          |

| 0EH                       | REG_USB_H_CTRL     | USB host control register                                                                                                                                                                                                                                  | 00000000 |

| 0EH bit 7                 | BIT_HOST_RECV_TOG  | Host receive synchronous flag:<br>0=DATA0; 1=DATA1                                                                                                                                                                                                         | 0        |

| 0EH bit 6                 | BIT_HOST_TRAN_TOG  | Host transmit synchronous flag:<br>0=DATA0; 1=DATA1                                                                                                                                                                                                        | 0        |

| 0EH bit 5                 | Reserved           | The data read is meaningless and must be 0                                                                                                                                                                                                                 | 0        |

| 0EH bit 4                 | Reserved           | The data read is meaningless and must be 0                                                                                                                                                                                                                 | 0        |

| 0EH bit 3                 | BIT_HOST_START     | Host transmission start control:<br>0=pause; 1=transmission enabled, automatically<br>cleared to 0 after completion                                                                                                                                        | 0        |

| 0EH bit 2<br>to 0EH bit 0 | Reserved           | The data read is meaningless and must be 000                                                                                                                                                                                                               | 000      |

| 0FH-3FH                   | Reserved           | Disable reading and writing                                                                                                                                                                                                                                | ???????? |

| 40H-7FH                   | RAM_HOST_TRAN      | USB host transmit buffer                                                                                                                                                                                                                                   |          |

| C0H-FFH                   | RAM_HOST_RECV      | USB host receive buffer                                                                                                                                                                                                                                    |          |

| 80H-BFH                   | RAM_HOST_EXCH      | USB host backup buffer                                                                                                                                                                                                                                     |          |

### 6. Functional Specification

### 6.1. MCU Interfaces

CH370 chip supports general-purpose 8-bit passive parallel interface and SPI synchronous serial interface. During the power-on reset of CH370 chip, CH370 will sample the status of the CS#, WR# and RD# pins. If both WR# and RD# are at low level (grounded) and CS# is at the high (connected to the positive power source), select the SPI serial interface. Otherwise, select the parallel interface.

The interrupt request outputted by the CH370 chip INT# pin is active at the low level by default, and the MCU can learn the interrupt request of CH370 in the interrupt mode or query mode. To save pins, the MCU can directly query the interrupt flag register REG\_INTER\_FLAG of CH370 to learn the interrupt without being connected to the INT# pin of CH370.

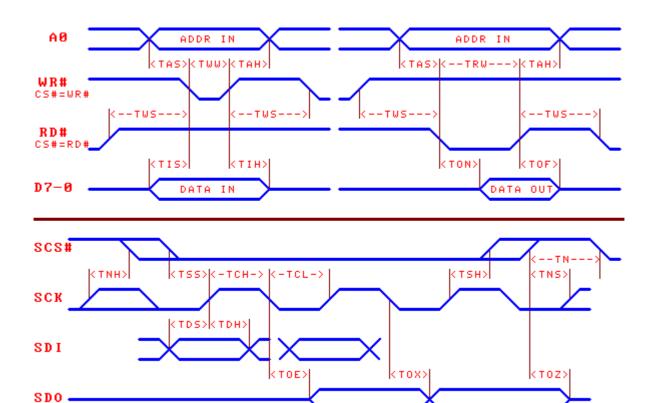

#### **6.2.** Parallel Interfaces

The parallel port signal lines include: 8-bit bidirectional data buses  $D7 \sim D0$ , read strobe input pin RD#, write strobe input pin WR#, chip selection input pin CS# and address input pin A0.

For the MCU similar to the Intel parallel port time sequence, the RD# and WR# pins of the CH370 chip can be connected to the read strobe output pin and write strobe output pin of the MCU respectively. For the

MCU similar to Motorola parallel port time sequence, the RD# pin of the CH370 chip shall be connected to the low level, and the WR# pin shall be connected to the reading and writing direction output pin R/-W of the MCU.

The following table shows the true values of the parallel port I/O operation (X in the table means that this bit is not concerned, and Z means that CH370 tri-status is disabled).

| CS# | WR# | RD# | A0                                                                                                                                            | D7-D0  | Actual operation on CH370 chip                                                                                                                              |  |  |

|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | 0   | 0   | Х                                                                                                                                             | X/Z    | Sampling is started for selecting SPI port mode during the power-on reset of CH370 chip                                                                     |  |  |

| 1   | Х   | Х   | Х                                                                                                                                             | X/Z    | CH370 is not selected, and no any operation is made                                                                                                         |  |  |

| 0   | 1   | 1   | Х                                                                                                                                             | X/Z    | Although selected, no any operation is made                                                                                                                 |  |  |

| 0   | 0   | 1/X | 1                                                                                                                                             | Input  | Write the index address to CH370, which is the starting address for subsequent reading and writing operations                                               |  |  |

| 0   | 0   | 1/X | 0                                                                                                                                             | Input  | Write data to the specified address, and the index address will<br>increase progressively after completion, facilitating continuous<br>reading and writing  |  |  |

| 0   | 1   | 0   | 0                                                                                                                                             | Output | Read data from the specified address. The index address will<br>increase progressively after completion, facilitating the continuous<br>reading and writing |  |  |

| 0   |     |     | Read data from the specified address. The index address remains<br>unchanged, facilitating the reading and writing back after<br>modification |        |                                                                                                                                                             |  |  |

CH370 chip occupies two address bits. When the A0 pin is at high level, select the index address port, and you can write a new index address, or read data but keep the index address unchanged Select the data port when the A0 pin is at the low level. You can read and write the data corresponding to the index address, and automatically add 1 to the index address after the reading and writing operation is completed to facilitate the continuous reading and writing of the next data. The steps for the MCU to read and write to the CH370 chip through an 8-bit parallel port are: Firstly, write the index address from the index address port, and then read and write several data continuously.

The auto-increment of index address is only applicable to the buffer areas with address no less than 40H, and not applicable to registers with address less than 40H.

#### 6.3. SPI

The SPI synchronous serial interface signal lines include: SPI chip selection input pin SCS#, serial clock input pin SCK, serial data input pin SDI and serial data output pin SDO.

The SCS# pin of the CH370 chip is driven by the SPI chip selection output pin or the general output pin of the MCU. The SCK pin is driven by the SPI clock output pin SCK of the MCU. The SDI pin is driven by the SPI data output pin SDO or MOSI, and SDO pin is connected to the SPI data input pin SDI or MISO of the MCU. For the hardware SPI interface, it is recommended that the SPI setting is CPOL=CPHA=0 or CPOL=CPHA=1, and the data bit sequence is MSB first.

The SPI interface of CH370 supports the MCU to simulate SPI interface for communication with the common I/O pins. The SDO of CH370 is a three-status output pin, which will only output after receiving a reading operation command. To save pins, the SDO pin of CH370 can be connected in parallel with the SDI pin and then connected to the bidirectional I/O pin of the MCU. It is recommended that the SDO pin of CH370 shall be connected to the SDI pin in series with a few hundred ohms.

The SPI interface of CH370 supports SPI mode 0 and SPI mode 3. CH370 always inputs data from the rising

edge of the SPI clock SCK, and outputs data from the falling edge of SCK when the output is allowed. The data bit sequence is MSB first, and 8 full bits are a byte.

Operation procedure of SPI:

- ① The MCU generates the SPI chip selection of CH370 chip, which is active at low level;

- ② The MCU sends out a one-byte address code according to the SPI output mode, which is used to specify the initial address of subsequent reading and writing operations;

- ③ The MCU sends out a one-byte command code to indicate the operation direction. The reading operation command code is C0H, and the writing operation command code is 80H;