# Ethernet Protocol Stack Chip CH395

Datasheet 1 Version: 2.2 https://wch-ic.com

# 1. Overview

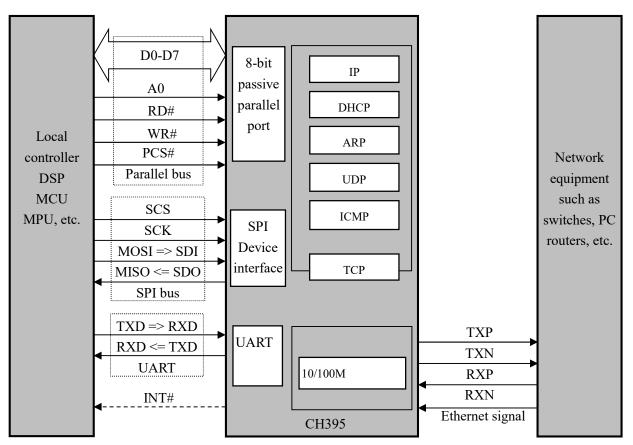

CH395 is an Ethernet protocol stack management chip, which is used for Ethernet communication in MCU system.

CH395 chip comes with 10/100M Ethernet Media Access Control (MAC) and Physical layer (PHY), which is fully compatible with IEEE802.3 protocol, and has built-in Ethernet protocol stack firmware such as IP, ARP, ICMP, UDP and TCP. MCU system can conveniently communicate with the network through CH395 chip.

CH395 supports 3 communication interfaces: 8-bit parallel port, SPI interface and UART. Controllers such as MCU/DSP/MCU/MPU can control the CH395 chip for Ethernet communication through any of the above communication interfaces.

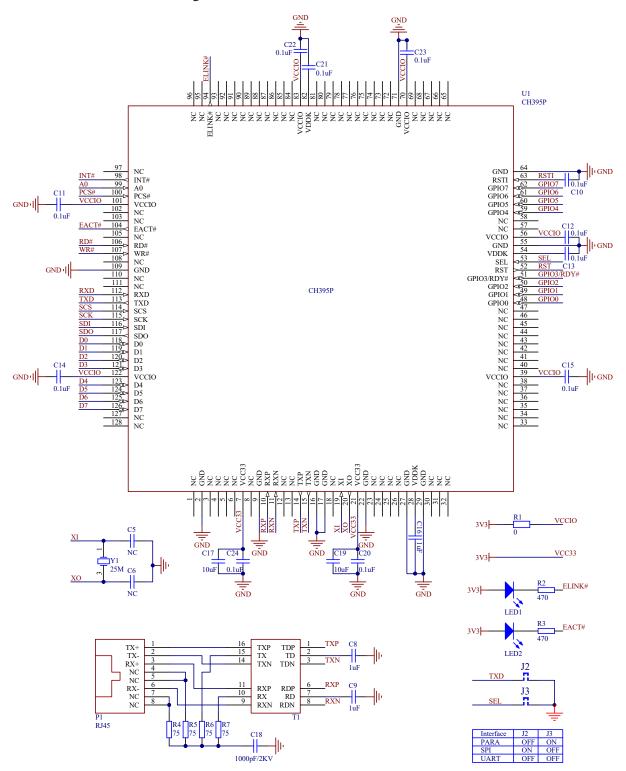

The following figure shows the application block diagram of CH395.

Figure 1-1 CH395 application block diagram

## 2. Features

- Built-in Ethernet Media Access Control (MAC) and Physical layer (PHY)

- Support 10/100M, full-duplex/half-duplex adaptation, and is compatible with IEEE802.3 protocol

- Support automatic conversion of MDI/MDIX lines

- I/O port supports 3.3V, 2.5V and 1.8V power supply, and is compatible with various voltage standards MCU.

- Built-in network port pull-up resistor, crystal oscillator matching capacitor, simplify peripheral circuits.

- Built-in TCP/IP protocol suite. Support IPv4, ARP, ICMP, UDP and TCP protocols

- Support DHCP to automatically obtain IP address.

- Provide 8 independent Socket pairs, which can transmit and receive data simultaneously.

- Support MACRAW mode and IPRAW mode.

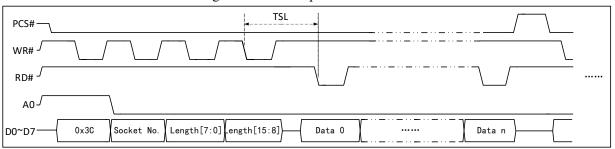

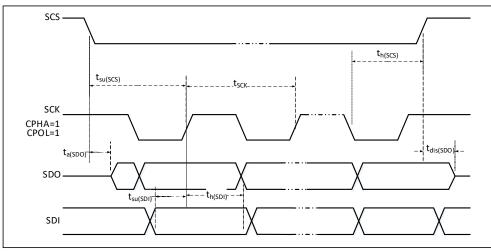

- Provide a SPI slave interface (SPI mode 0 or 3) up to 40MHz, with the high bit coming first

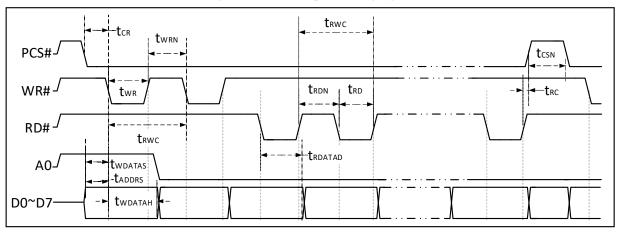

- Provide high-speed 8-bit passive parallel interface and support parallel data bus connected to MCU.

- Provide UART with speeds up to 10Mbps, supports serial port connected to MCU, and supports dynamic adjustment of communication baud rate

- CH395F serial port supports RS485 automatic switching, and supports hardware flow control

- Support Sleep mode

- Built-in 24K RAM can be used for Ethernet data transceiver, and each Socket transceiver buffer can be configured flexibly

- Built-in 4KB EEPROM

- Support 8-channel GPIO

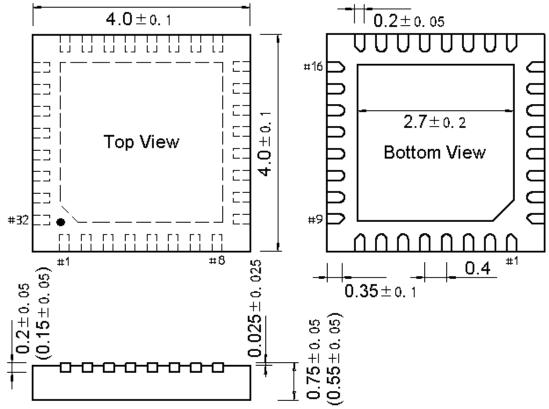

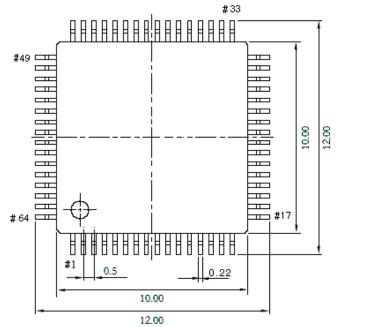

- Provide QFN32, LQFP64M and LQFP128 lead-free packages.

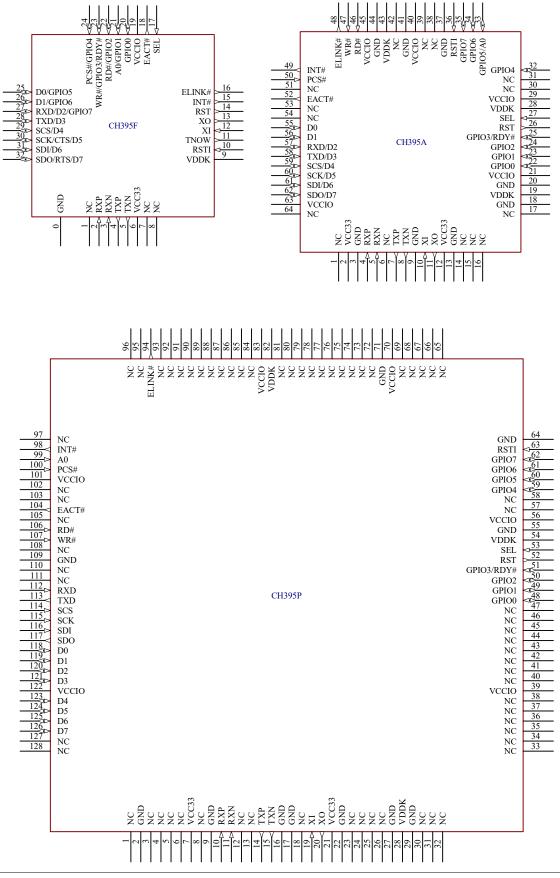

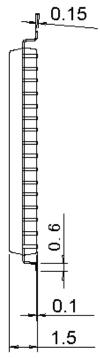

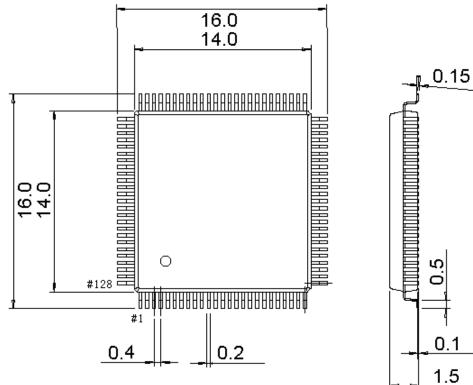

# 3. Package

| Package Form | Body Size | Pin Pitch     |  | Package Description           | Order Model |

|--------------|-----------|---------------|--|-------------------------------|-------------|

| QFN32        | 4*4mm     | 0.4mm 15.7mil |  | Quad Flat No-leads Package    | CH395F      |

| LQFP64M      | 10*10mm   | 0.5mm 19.7mil |  | Low-profile Quad Flat Package | CH395A      |

| LQFP128      | 14*14mm   | 0.4mm 15.7mil |  | Low-profile Quad Flat Package | CH395P      |

Note: 1. It is recommended to use smaller package CH395F for new design.

2 CH395A based on CH395Q upgrade, CH395P based on CH395L upgrade, the pin is basically compatible, replacement needs to adjust the peripheral circuit.

3. CH395Q, CH395L maintain the supply but not recommended for new designs.

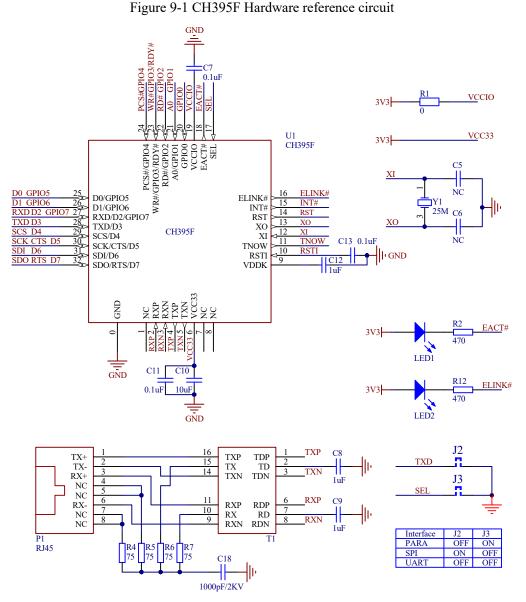

# 4. CH395F Pins

# 4.1 CH395F Pin Definition

| CH395F  |           |                     |                                                                                                                 |  |  |

|---------|-----------|---------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| Pin No. | Pin Name  | Type <sup>(1)</sup> | Pin Description <sup>(2)</sup>                                                                                  |  |  |

| 2       | RXP       |                     | Differential input in 10BASE-T/100BASE-TX MDI mode;                                                             |  |  |

| 3       | RXN       | I/()                | Differential output in 10BASE-T/100BASE-TX MDI mode,                                                            |  |  |

| 4       | ТХР       |                     | Differential output in 10BASE-T/100BASE-TX MDIX mode;                                                           |  |  |

| 5       | TXN       | I/O                 | Differential input in 10BASE-T/100BASE-TX MDI mode,                                                             |  |  |

| 5       | 1211      |                     | 3.3V power supply input, it is recommended to place 0.1uF parallel 10uF                                         |  |  |

| 6       | VCC33     | Р                   | or 4.7uF ground capacitor close to the core.                                                                    |  |  |

| 19      | VCCIO     | Р                   | For the power input of I/O interface, it is recommended to place 0.1uF capacitance to ground close to the chip. |  |  |

| 9       | VDDK      | Р                   | The external 1uF ground capacitor is placed close to the chip.                                                  |  |  |

| 0       | GND       |                     | Common ground.                                                                                                  |  |  |

| 1/7/8   | NC        |                     | Reserved, suggested suspension.                                                                                 |  |  |

| 1///0   | 110       |                     | The crystal oscillator input needs an external 25MHz crystal end or an                                          |  |  |

| 12      | XI        | Ι                   | external clock input with a built-in crystal oscillator matching capacitor.                                     |  |  |

|         |           |                     | The inverted output of the crystal oscillator needs to be externally                                            |  |  |

| 13      | XO        | 0                   | connected to the other end of the 25MHz crystal, and a crystal oscillator                                       |  |  |

| 10      | no        |                     | matching capacitor is built in.                                                                                 |  |  |

| 10      | RSTI      |                     | External reset input, active low, built-in pull-up resistor.                                                    |  |  |

| 11 TNOW |           | 0                   | Transmit status output, which is used to control RS485 transceiver                                              |  |  |

|         |           |                     | switching of serial port.                                                                                       |  |  |

| 14      | RST       | 0                   | Reset and external reset output, active high.                                                                   |  |  |

| 15      | INT#      | 0                   | Interrupt request output, active low.                                                                           |  |  |

|         |           |                     | Network connection indicator LED output:                                                                        |  |  |

| 16      | ELINK#    | 0                   | Low level indicates that Ethernet PHY is connected;                                                             |  |  |

|         |           |                     | High level indicates that Ethernet PHY is not connected.                                                        |  |  |

| 17      | CEI       | יותו                | Used as an interface configuration input during internal chip reset. For                                        |  |  |

| 17      | SEL       | I,PU                | details on the specific configuration method, please refer to Chapter 6.1.                                      |  |  |

| 10      | ЕАСТ#     | 0                   | Carrier sensing indicator LED output:                                                                           |  |  |

| 18      | EACT# O   |                     | LED flashes indicate a carrier sensing signal.                                                                  |  |  |

| 20      | GPIO0     | I/O                 | General input and output pin 0, configured as input by default.                                                 |  |  |

|         |           |                     | A0: Address input of parallel port, distinguishing command port from                                            |  |  |

|         |           |                     | data port, built-in pull-up resistor; When A0=1, you can write commands,                                        |  |  |

| 21      | A0/GPIO1  |                     | and when A0=0, you can read and write data.                                                                     |  |  |

|         |           |                     | GPIO1: General-purpose input and output pin 1, configured as input by                                           |  |  |

|         |           |                     | default.                                                                                                        |  |  |

| 22      | RD#/GPIO2 | I/O,PU              | RD#: The parallel port read gate input, active low, built-in pull-up                                            |  |  |

| 22      |           | 10,10               | resistor.                                                                                                       |  |  |

Table 4-1 CH395F pin definition

|    |                    |        | GPIO2: General-purpose input and output pin 2, configured as input by                                         |

|----|--------------------|--------|---------------------------------------------------------------------------------------------------------------|

|    |                    |        | default.                                                                                                      |

|    |                    |        | WR#: The parallel port write gate input, active low, built-in pull-up resistor.                               |

| 23 | WR#/GPIO3/RD<br>Y# | I/O,PU | GPIO3: General-purpose input and output pin 3, configured as input by default.                                |

|    | 1 77               |        | RDY#: Output low level after CH395F reset is completed; RDY#                                                  |

|    |                    |        | function is not effective in parallel port mode.                                                              |

|    |                    |        | PCS#: Chip selection control signal input of parallel port, active low level, built-in pull-up resistor.      |

| 24 | PCS#/GPIO4         | I/O,PU | GPIO4: General-purpose input and output pin 4, configured as input by                                         |

|    |                    |        | default.                                                                                                      |

|    |                    |        | D0: The 0th bit in the 8-bit bidirectional data bus with a parallel port,                                     |

| 25 | D0/GPIO5           | I/O,PU | built-in pull-up resistor.                                                                                    |

| 25 | D0/01105           | 10,10  | GPIO5: General-purpose input and output pin 5, configured as input by                                         |

|    |                    |        | default.                                                                                                      |

|    |                    |        | D1: The first bit in the 8-bit bidirectional data bus with a parallel port, with a built-in pull-up resistor. |

| 26 | D1/GPIO6           | I/O,PU | GPIO6: General-purpose input and output pin 6, configured as input by                                         |

|    |                    |        | default.                                                                                                      |

|    |                    |        | RXD: Serial data input of UART, built-in pull-up resistor;                                                    |

|    | RXD/D2/GPIO7       | I/O,PU | D2: The second bit in the 8-bit bidirectional data bus with a parallel port,                                  |

| 27 |                    |        | built-in pull-up resistor.                                                                                    |

|    |                    |        | GPIO7: General-purpose input and output pin 7, configured as input by                                         |

|    |                    |        | default.<br>During the internal reset of the chip, the interface configuration input is                       |

|    |                    |        | input, and the built-in pull-up resistor is used in Chapter 6.1. After the                                    |

| •  | TXD/D3             | I/O,PU | chip reset is completed, use it as an interface pin.                                                          |

| 28 |                    |        | TXD: Serial data output of asynchronous serial port.                                                          |

|    |                    |        | D3: The third bit in the 8-bit bidirectional data bus with a parallel port,                                   |

|    |                    |        | built-in pull-up resistor.                                                                                    |

|    |                    |        | SCS: Chip-select input SCS of the SPI interface, active low, built-in                                         |

| 29 | SCS/D4             | I/O,PU | pull-up resistor.                                                                                             |

|    |                    |        | D4: The 4th bit in the 8-bit bidirectional data bus with a parallel port, built-in pull-up resistor.          |

|    |                    |        | SCK: The serial clock input SCK of the SPI interface, built-in pull-up                                        |

|    |                    |        | resistor.                                                                                                     |

|    |                    |        | CTS: Clear the send input, built-in pull-up resistor. If it is high, the serial                               |

|    | SCK/CTS/D5         |        | port blocks the next data transmission when the current data transmission                                     |

| 30 |                    | I/O,PU | is over. You can connect to the countertop RTS to achieve hardware flow                                       |

|    |                    |        | control (the serial port flow control function is turned off by default and                                   |

|    |                    |        | can be turned on through the CMD_SET_FUN_PARA command).                                                       |

|    |                    |        | D5: The 5th bit in the 8-bit bidirectional data bus with a parallel port, built-in pull-up resistor.          |

|    |                    |        | ount-in puil-up rosisior.                                                                                     |

|           |               |            |                                                                           | SDI: Serial data input to SDI of the SPI interface, built-in pull-up resistor.   |  |

|-----------|---------------|------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| 31 SDI/D6 | SDI/D6        | I/O,PU     | D6: The 6th bit in the 8-bit bidirectional data bus with a parallel port, |                                                                                  |  |

|           |               |            |                                                                           | built-in pull-up resistor.                                                       |  |

|           | 32 SDO/RTS/D7 |            | SDO: Serial data output as SPI interface.                                 |                                                                                  |  |

|           |               |            | I/O,PU                                                                    | RTS: Transmit request output. If it is low, it indicates that the serial port is |  |

|           |               |            |                                                                           | ready to receive data. You can connect to the countertop CTS to achieve          |  |

|           |               | SDO/RTS/D7 |                                                                           | hardware flow control (the serial port flow control function is turned off       |  |

|           |               |            |                                                                           | by default and can be turned on through the CMD_SET_FUN_PARA                     |  |

|           |               |            |                                                                           | command).                                                                        |  |

|           |               |            |                                                                           | D7: The 7th bit in the 8-bit bidirectional data bus with a parallel port,        |  |

|           |               |            |                                                                           | built-in pull-up resistor.                                                       |  |

*Note 1: Table abbreviation explanation:*

*I* = *Input*; *O* = *Output*; *I*/*O* = *Input*/*Output*;

*P* = *Power supply; PU* = *Built-in pull-up resistor.*

Note 2: The specific function of the alternate pin of the CH395F depends on the currently selected interface mode. When the alternate pin is used for the interface function, its GPIO function will be occupied, causing its GPIO function to fail, and at the same time, the corresponding bits in the GPIO register have no practical significance.

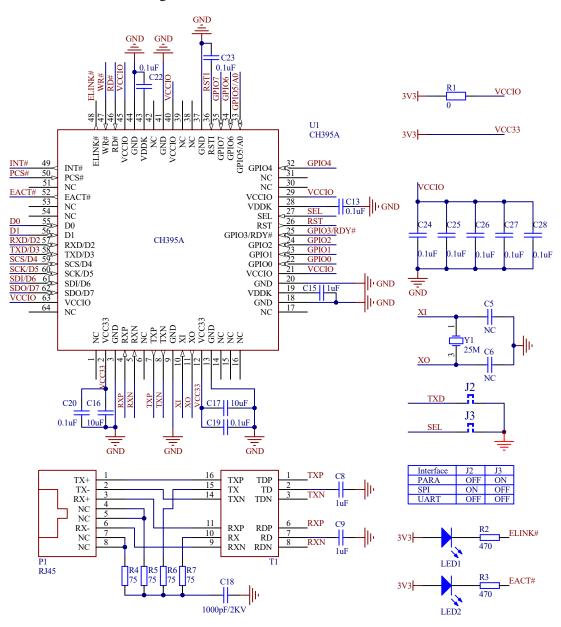

# 4.2 CH395A Pin Definition

| Table 4-2 CH395A pin definition | n definition | e 4-2 CH395A pi |

|---------------------------------|--------------|-----------------|

|---------------------------------|--------------|-----------------|

| CTION 5                                            |                |                     |                                                                                                                                                                                |  |

|----------------------------------------------------|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CH395A<br>Pin No.                                  | Pin Name       | Type <sup>(1)</sup> | Pin Description <sup>(2)</sup>                                                                                                                                                 |  |

| 4                                                  | RXP            | I/O                 | Differential input in 10BASE-T/100BASE-TX MDI mode;                                                                                                                            |  |

| 5                                                  | RXN            | 1/0                 | Differential output in 10BASE-T/100BASE-TX MDIX mode.                                                                                                                          |  |

| 7                                                  | ТХР            | I/O                 | Differential output in 10BASE-T/100BASE-TX MDI mode;                                                                                                                           |  |

| 8                                                  | TXN            |                     | Differential input in 10BASE-T/100BASE-TX MDIX mode.                                                                                                                           |  |

| 2/12                                               | VCC33          | Р                   | 3.3V power supply input, it is recommended that 0.1uF parallel 10uF or 4.7uF ground capacitor be placed close to the chip.                                                     |  |

| 21/29/40/45/63                                     | VCCIO          | Р                   | For the power input of the I/O interface, it is recommended to place the 0.1uF ground capacitor close to the chip.                                                             |  |

| 19                                                 | VDDK           | Р                   | The external 1uF ground capacitor is placed close to the chip.                                                                                                                 |  |

| 28/43                                              | VDDK           | Р                   | The external 0.1uF ground capacitor is placed close to the chip.                                                                                                               |  |

| 3/9/13/18/20/37/<br>41/44                          | GND            | Р                   | Common ground.                                                                                                                                                                 |  |

| 1/6/14/15/16/17/<br>30/31/38/39/42/<br>51/53/54/64 | NC             | -                   | Reserved, suggested suspension.                                                                                                                                                |  |

| 10                                                 | XI             | Ι                   | The crystal oscillator input needs an external 25MHz crystal end or an external clock input with a built-in crystal oscillator matching capacitor.                             |  |

| 11                                                 | ХО             | О                   | The inverted output of the crystal oscillator needs to be externally connected to the other end of the 25MHz crystal, and a crystal oscillator matching capacitor is built in. |  |

| 22                                                 | GPIO0          | I/O                 | General-purpose input and output pin 0, configured as input by default.                                                                                                        |  |

| 23                                                 | GPIO1          | I/O                 | General-purpose input and output pin 1, configured as input by default.                                                                                                        |  |

| 24                                                 | GPIO2          | I/O                 | General-purpose input and output pin 2, configured as input by default.                                                                                                        |  |

| 25                                                 | GPIO3/RDY<br># | I/O                 | GPIO3: General-purpose input and output pin 3, configured as input by default.<br>RDY#: After CH395A is reset, the output is low.                                              |  |

| 26                                                 | RST            | 0                   | Power-on reset and external reset output, active high level.                                                                                                                   |  |

| 27                                                 | SEL            | I,PU                | Used as an interface configuration input during internal chip reset. For details on the specific configuration method, please refer to Chapter 6.1.                            |  |

| 32                                                 | GPIO4          | I/O                 | General-purpose input and output pin 4, configured as input by default.                                                                                                        |  |

| 33                                                 | GPIO5/A0       | I/O,PU              | GPIO5: General-purpose input and output pin 5, configured as input b<br>default.<br>A0: The address input of the parallel port is distinguished from th                        |  |

| 34                                                 | GPIO6          | I/O                 |                                                                                                                                                                                |  |

|                                                    |                |                     |                                                                                                                                                                                |  |

| 35 | GPIO7  | I/O    | General-purpose input and output pin 7, configured as input by default.                                                                                                                                                                                                                                      |  |

|----|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 36 | RSTI   | I,PU   | External reset input, active low, built-in pull-up resistor.                                                                                                                                                                                                                                                 |  |

| 46 | RD#    | I,PU   | The parallel port read gate input, active low, built-in pull-up resistor.                                                                                                                                                                                                                                    |  |

| 47 | WR#    | I,PU   | The parallel port write gate input, active low, built-in pull-up resistor.                                                                                                                                                                                                                                   |  |

| 49 | INT#   | 0      | Interrupt request output, active low.                                                                                                                                                                                                                                                                        |  |

| 50 | PCS#   | I,PU   | The chip select control input of parallel port, active low, built-in pull-up resistor.                                                                                                                                                                                                                       |  |

| 55 | D0     | I/O,PU | The 0th bit in the 8-bit bidirectional data bus with a parallel port, built-in pull-up resistor.                                                                                                                                                                                                             |  |

| 56 | D1     | I/O,PU | The 1st bit in the 8-bit bidirectional data bus with a parallel port, built-in pull-up resistor.                                                                                                                                                                                                             |  |

| 57 | RXD/D2 | I/O,PU | RXD: Serial data input of UART, built-in pull-up resistor;<br>D2: The 2nd bit in the 8-bit bidirectional data bus with a parallel port,<br>built-in pull-up resistor.                                                                                                                                        |  |

| 58 | TXD/D3 | I/O,PU | During the internal reset of the chip, the interface configuration inpinput, and the built-in pull-up resistor is used in Chapter 6.1. After chip reset is completed, use it as an interface pin.<br>TXD: Serial data output of UART.<br>D3: The 3rd bit in the 8-bit bidirectional data bus with a parallel |  |

| 59 | SCS/D4 | I/O,PU | built-in pull-up resistor.<br>SCS: Chip-select input SCS of the SPI interface, active low level,<br>built-in pull-up resistor.<br>D4: The 4th bit in the 8-bit bidirectional data bus with a parallel port,<br>built-in pull-up resistor.                                                                    |  |

| 60 | SCK/D5 | I/O,PU | SCK: Serial clock input SCK of SPI interface, built-in pull-up resistor.<br>D5: The 5th bit in the 8-bit bidirectional data bus with a parallel port<br>built-in pull-up resistor.                                                                                                                           |  |

| 61 | SDI/D6 | I/O,PU | SDI: Serial data input SDI of SPI interface, built-in pull-up resistor.<br>D6: The 6th bit in the 8-bit bidirectional data bus with a parallel port,<br>built-in pull-up resistor.                                                                                                                           |  |

| 62 | SDO/D7 | I/O,PU | SDO: Serial data output as SPI interface.<br>J D7: The 7th bit in the 8-bit bidirectional data bus with a parallel por<br>built-in pull-up resistor.                                                                                                                                                         |  |

| 48 | ELINK# | О      | Network connection indicator LED output:<br>Low level indicates that Ethernet PHY is connected;<br>High level indicates that Ethernet PHY is not connected.                                                                                                                                                  |  |

| 52 | EACT#  | 0      | Carrier induction indicates LED output:<br>LED flashing indicates carrier induction signal.                                                                                                                                                                                                                  |  |

*Note 1: Table abbreviation explanation:*

I = Input; O = Output; I/O = Input/Output;

*P* = *Power supply; PU* = *Built-in pull-up resistor.*

Note 2: The specific function of the CH395A's alternate pins depends on the currently selected interface mode. When the alternate pin is used for the interface function, its GPIO function will be occupied, resulting in its GPIO function being invalid and the corresponding bit in the GPIO register having no practical meaning.

# 4.3 CH395P Pin Definition

| CH395P<br>Pin No.                                                                                                                                                                                                                                                 | Pin Name | Type <sup>(1)</sup> | Pin Description                                                                                                                                                                |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 10                                                                                                                                                                                                                                                                | RXP      |                     | Differential input in 10BASE-T/100BASE-TX MDI mode;                                                                                                                            |  |  |  |  |

| 11                                                                                                                                                                                                                                                                | RXN      | I/O                 | Differential output in 10BASE-T/100BASE-TX MDIX mode.                                                                                                                          |  |  |  |  |

| 14                                                                                                                                                                                                                                                                | TXP      |                     | Differential output in 10BASE-T/100BASE-TX MDI mode;                                                                                                                           |  |  |  |  |

| 15                                                                                                                                                                                                                                                                | TXN      | I/O                 | Differential input in 10BASE-T/100BASE-TX MDIX mode.                                                                                                                           |  |  |  |  |

| 7/21                                                                                                                                                                                                                                                              | VCC33    | Р                   | 3.3V power supply input, it is recommended to place 0.1uF parallel<br>10uF or 4.7uF ground capacitor close to the core.                                                        |  |  |  |  |

| 39/56/70/83/101<br>/122                                                                                                                                                                                                                                           | VCCIO    | Р                   | For the power input of I/O interface, it is recommended to place 0.1uF capacitance to ground close to the chip.                                                                |  |  |  |  |

| 28                                                                                                                                                                                                                                                                | VDDK     | Р                   | The external 1uF ground capacitor is placed close to the chip.                                                                                                                 |  |  |  |  |

| 54/82                                                                                                                                                                                                                                                             | VDDK     | Р                   | The external 0.1uF ground capacitor is placed close to the chip.                                                                                                               |  |  |  |  |

| 2/9/16/17/22/27/<br>29/55/64/71/109                                                                                                                                                                                                                               | GND      | Р                   | Common ground.                                                                                                                                                                 |  |  |  |  |

| 1/3/4/5/6/8/12/1<br>3/18/23/24/25/2<br>6/30/31/32/33/3<br>4/35/36/37/38/4<br>0/41/42/43/44/4<br>5/46/47/57/58/6<br>5/66/67/68/69/7<br>2/73/74/75/76/7<br>7/78/79/80/81/8<br>4/85/86/87/88/8<br>9/90/91/92/93/9<br>5/96/97/102/103<br>/105/108/110/11<br>1/127/128 | NC       | -                   | Reserved, suggested suspension.                                                                                                                                                |  |  |  |  |

| 19                                                                                                                                                                                                                                                                | XI       | Ι                   | The crystal oscillator input needs an external 25MHz crystal end or an external clock input with a built-in crystal oscillator matching capacitor.                             |  |  |  |  |

| 20                                                                                                                                                                                                                                                                | ХО       | О                   | The inverted output of the crystal oscillator needs to be externally connected to the other end of the 25MHz crystal, and a crystal oscillator matching capacitor is built in. |  |  |  |  |

| 48                                                                                                                                                                                                                                                                | GPIO0    | I/O                 | General-purpose input and output pin 0, configured as input by default.                                                                                                        |  |  |  |  |

| 49                                                                                                                                                                                                                                                                | GPIO1    | I/O                 | General-purpose input and output pin 1, configured as input by default.                                                                                                        |  |  |  |  |

| 50                                                                                                                                                                                                                                                                | GPIO2    | I/O                 | General-purpose input and output pin 2, configured as input by default.                                                                                                        |  |  |  |  |

|         |           |        | GPIO3: General-purpose input and output pin 3, configured as input          |  |  |  |

|---------|-----------|--------|-----------------------------------------------------------------------------|--|--|--|

| 51      | GPIO3/RDY | I/O    | by default.                                                                 |  |  |  |

| 51      | #         |        | RDY#: After CH395P is reset, the output is low.                             |  |  |  |

| 52      | RST       | 0      | Power-on reset and external reset output, active high level.                |  |  |  |

| 52      | KST       |        | Used as an interface configuration input during internal chip reset. For    |  |  |  |

| 53      | SEL       | I,PU   | details on the specific configuration method, please refer to Chapter       |  |  |  |

| 55      | SEE       | 1,1 0  | 6.1.                                                                        |  |  |  |

|         |           |        | General-purpose input and output pin 4, configured as input by              |  |  |  |

| 59      | GPIO4     | I/O    | default.                                                                    |  |  |  |

| 60      | GPIO5     | I/O    | General-purpose input and output pin 5, configured as input by              |  |  |  |

| 00      |           |        | default.                                                                    |  |  |  |

| 61      | GPIO6     | I/O    | General-purpose input and output pin 6, configured as input by              |  |  |  |

|         |           |        | default.                                                                    |  |  |  |

| 62      | GPIO7     | I/O    | General-purpose input and output pin 7, configured as input by              |  |  |  |

|         |           |        | default.                                                                    |  |  |  |

| 63      | RSTI      | I,PU   | External reset input, active low, built-in pull-up resistor.                |  |  |  |

| 98      | INT#      | 0      | Interrupt request output, active low.                                       |  |  |  |

|         | A0        | I,PU   | Address input of parallel port, distinguishing command port from data       |  |  |  |

| 99      |           |        | port, built-in pull-up resistor;                                            |  |  |  |

|         |           |        | When A0=1, the command can be written, and when A0=0, the data              |  |  |  |

|         |           |        | can be read and written.                                                    |  |  |  |

| 100     | PCS#      | I,PU   | Chip selection control input of parallel port, active low, built-in         |  |  |  |

|         |           |        | pull-up resistor.                                                           |  |  |  |

| 106     | RD#       | I,PU   | Read strobe input of parallel port, active low, built-in pull-up resistor.  |  |  |  |

| 107     | WR#       | I,PU   | Write strobe input of parallel port, active low, built-in pull-up resistor. |  |  |  |

| 112     | RXD       | I,PU   | Serial data input of UART with built-in pull-up resistor.                   |  |  |  |

|         |           |        | During the internal reset of the chip, the input is configured for the      |  |  |  |

|         |           |        | interface, and the pull-up resistor is built in. For the configuration      |  |  |  |

| 113     | TXD       | I/O    | method, please refer to Chapter 6.1.                                        |  |  |  |

|         |           |        | After the chip reset is completed, it is the serial data output of          |  |  |  |

|         |           |        | asynchronous serial port.                                                   |  |  |  |

| 114     | SCS       | I,PU   | Chip selection input of SPI interface, active low, built-in pull-up         |  |  |  |

|         |           | -,     | resistor.                                                                   |  |  |  |

| 115     | SCK       | I,PU   | Serial clock input of SPI interface, built-in pull-up resistor.             |  |  |  |

| 116     | SDI       | I,PU   | Serial data input of SPI interface, built-in pull-up resistor.              |  |  |  |

| 117     | SDO       | 0      | Serial data output of SPI interface.                                        |  |  |  |

| 118~121 | D0 ~ D7   | I/O,PU | PU Parallel port 8-bit bidirectional data bus, built-in pull-up resistor.   |  |  |  |

| 123~126 |           |        |                                                                             |  |  |  |

|         |           |        | Network connection indicator LED output:                                    |  |  |  |

| 94      | ELINK#    | 0      | Low level indicates that Ethernet PHY is connected;                         |  |  |  |

|         |           |        | High level indicates that Ethernet PHY is not connected.                    |  |  |  |

| 104     | EACT#     | Ο      | Carrier induction indicates LED output:                                     |  |  |  |

|         | EAU1#     |        | LED flashing indicates carrier induction signal.                            |  |  |  |

Note 1: Table abbreviation explanation:

*I* = *Input; O* = *Output; I/O* = *Input/Output; P* = *Power supply; PU* = *Built-in pull-up resistor.*

## 5. Command

The data in this datasheet, the suffix B or b is a binary number, and the suffix H is a hexadecimal number, otherwise it is a decimal number.

The double-word data with the lower byte in front (Little-Endian) (32 bits in total) refers to: first the lowest byte (bits 7 to 0), then the lower byte (bits 15 to 8), then the higher byte (bits 23 to 16), and finally the highest byte (bits 31 to 24).

A data stream refers to a data block composed of several consecutive bytes, with a minimum total length of 0.

The numbers in the brackets of the input data and output data in the following table are the number of bytes of the parameter, and if there is no bracket, the default is 1 byte.

The MCU referred to in this datasheet is basically suitable for DSP or MCU/MPU/SCM, etc.

Socket Pair contains quadruples of source IP, source port, destination IP and destination port, which can uniquely determine the 2 connections in the Internet. This manual is referred to as Socket. CH395 can provide 8 Sockets at the same time, and their index values are 0, 1, 2, 3, 4, 5, 6, and 7 respectively.

The IP and MAC addresses agreed upon in this manual may differ from some documents for convenience only:

If the IP address is 192.168.1.2, where 192 is the lowest byte and 2 is the highest byte. This article says (IP) low bytes are in front.

If the MAC address is 00.01.02.03.04.05, 00 is the lowest byte and 05 is the highest byte. This paper calls (MAC) low byte first.

In this datasheet, all commands containing IP address input or output are in byte order with IP low byte first.

In this datasheet, all commands containing MAC address input or output are in byte order with MAC low byte first.

| Code | Command name CMD_           | Input data                | Output data                    | Command purpose                                 |

|------|-----------------------------|---------------------------|--------------------------------|-------------------------------------------------|

| 01H  | GET_IC_VER                  |                           | Version number                 | Get the chip and firmware version               |

| 02H  | SET_BAUDRATE                | Baud rate coefficient (3) | Operating state                | Set the serial port communication baud rate     |

| 03H  | ENTER_SLEEP                 |                           |                                | Enter low-power sleep suspend state             |

| 05H  | RESET_ALL                   |                           | (Wait 15ms)                    | Perform a hardware reset                        |

| 06H  | CHECK_EXIST                 | Any data                  | Bitwise invert                 | Test communication interface and working status |

| 19H  | GET_GLOB_INT_STATUS<br>_ALL |                           | Global interrupt<br>status (2) | Get global interrupt status                     |

| 20H  | SET_PHY                     | PHY connection<br>method  |                                | Set the PHY connection method                   |

| 21H  | SET_MAC_ADDR                | MAC address (6)           |                                | Set MAC address                                 |

| 22H  | SET_IP_ADDR                 | IP address (4)            |                                | Set IP address                                  |

Table 5-1 Command list

| 23H   | SET GWIP ADDR            | Gateway address (4)  |                            | Set the gateway IP address                             |

|-------|--------------------------|----------------------|----------------------------|--------------------------------------------------------|

| 24H   | SET MASK ADDR            | Subnet mask (4)      |                            | Set subnet mask                                        |

| 2.111 |                          | Filter mode          |                            |                                                        |

| 25H   | SET MAC FILT             | HASH0(4)             | -                          | Set MAC filtering mode                                 |

| 2311  |                          | HASH1(4)             | -                          |                                                        |

| 26H   | GET_PHY_STATUS           |                      | PHY status                 | Get PHY status                                         |

| 27H   | INIT_CH395               |                      |                            | Initialize CH395 chip                                  |

| 2011  |                          |                      | Unreachable                | Get unreachable IP, port and                           |

| 28H   | GET_UNREACH_IPPORT       |                      | information (8)            | protocol                                               |

| 29H   | GET_GLOB_INT_STATUS      |                      | Global interrupt<br>status | Get global interrupt status                            |

| 2AH   | SET_RETRAN_COUNT         | Retry times          |                            | Set retry number, up to 20 times                       |

| 2BH   | SET_RETRAN_PERIOD        | Retry cycle (2)      |                            | Set retry period, up to 1000ms                         |

| 2CH   | GET_CMD_STATUS           |                      | Command execution status   | Get command execution status                           |

| 2DH   | GET_REMOT_IPP_SN         | Socket index         | IP and port (6)            | Get the IP and port of the remote<br>end (destination) |

| 2EH   | CLEAR_RECV_BUF_SN        | Socket index         |                            | Clear the receive buffer of Socket                     |

| 2FH   | GET_SOCKET_STATUS_S<br>N | Socket index         | Socket status              | Get Socket status                                      |

| 30H   | GET_INT_STATUS_SN        | Socket index         | Socket interrupt           | Get Socket interrupt status                            |

| 2111  | OFT ID ADDD ON           | Socket index         |                            | Set destination IP address of                          |

| 31H   | SET_IP_ADDR_SN           | Destination IP (4)   |                            | Socket.                                                |

| 32Н   | SET DES DODT SN          | Socket index         |                            | Set destination port address of                        |

| 3211  | SET_DES_PORT_SN          | Destination port (2) |                            | Socket.                                                |

| 33H   | SET SOUR PORT SN         | Socket index         |                            | Set source port of Socket                              |

| 5511  | SEI_SOUK_FORI_SN         | Source port (2)      |                            | Set source port of Socket                              |

| 34H   | SET PROTO TYPE SN        | Socket index         | _                          | Set operation mode of Socket                           |

| 5711  | SET_IKOTO_ITTE_SK        | Protocol type        |                            | Set operation mode of Socket                           |

| 35H   | OPEN_SOCKET_SN           | Socket index         |                            | Open Socket                                            |

| 36H   | TCP_LISTEN_SN            | Socket index         |                            | Enable Socket listening                                |

| 37H   | TCP_CONNECT_SN           | Socket index         |                            | Enable Socket connection                               |

| 38H   | TCP_DISCONNECT_SN        | Socket index         |                            | Disconnect the TCP connection of<br>Socket             |

|       |                          | Socket index         |                            |                                                        |

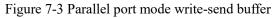

| 39H   | WRITE_SEND_BUF_SN        | Length (2)           |                            | Send buffer write data to Socket                       |

|       |                          | Data flow (N)        |                            |                                                        |

| 3BH   | GET_RECV_LEN_SN          | Socket index         | Length (2)                 | Gets Socket received data length                       |

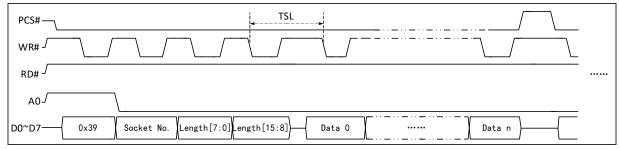

| 3CH   | READ RECV BUF SN         | Socket index         | Data flow (N)              | Receive data from Socket receive                       |

|       |                          | Length (2)           |                            | buffer                                                 |

| 3DH   | CLOSE_SOCKET_SN          | Socket index         |                            | Disable Socket                                         |

| 3EH   | SET IPRAW PRO SN         | Socket index         |                            | Set the protocol field of the IP                       |

|       |                          | IP protocol field    |                            | packet of Socket.                                      |

| 3FH   | PING_ENABLE                     | Enable flag            |                     | PING enable                      |

|-------|---------------------------------|------------------------|---------------------|----------------------------------|

| 40H   | GET_MAC_ADDR                    |                        | MAC address (6)     | Get MAC address                  |

| 41H   | DHCP ENABLE                     | Enable flag            |                     | Start (Stop) DHCP                |

| 42H   | GET_DHCP_STATUS                 |                        | DHCP status         | Get DHCP status                  |

| 4211  |                                 |                        | IP and other        | Get IP, MASK, DNS and other      |

| 43H   | GET_IP_INF                      |                        | information         | information.                     |

|       |                                 | ARP retransmission     |                     |                                  |

| 4 411 |                                 | period                 |                     | Set the ARP retransmission cycle |

| 44H   | SET_ARP                         | ARP retransmission     |                     | and times.                       |

|       |                                 | number                 |                     |                                  |

| 50H   | SET_TCP_MSS                     | TCP MSS (2)            |                     | Set TCP MSS                      |

| 51H   | SET_TTL                         | TTL                    |                     | Set TTL value, up to 128.        |

|       |                                 | Socket index           |                     |                                  |

| 52H   | SET_RECV_BUF                    | Start block address    |                     | Set Socket receive buffer        |

|       |                                 | Block number           |                     |                                  |

|       |                                 | Socket index           |                     |                                  |

| 53H   | SET_SEND_BUF                    | Start block address    |                     | Set Socket send buffer           |

|       |                                 | Block number           |                     |                                  |

| 55H   | SET_FUN_PARA                    | Function parameter (4) |                     | Set functional parameter         |

| 56H   | SET_KEEPALIVE_IDLE              | 4-byte time parameter  |                     | Set KEEPALIVE idle time          |

| 57H   | SET_KEEPALIVE_INTVL             | 4-byte time parameter  |                     | Set KEEPALIVE timeout            |

| 58H   | SET KEEPALIVE CNT               | Retry times            |                     | Set the number of KEEPALIVE      |

| 5611  | SEI_KEEIALIVE_CIVI              | iter y times           |                     | timeout retries                  |

| 59H   | SET_KEEPALIVE_SN                | Socket index           |                     | Set Socket KEEPALIVE             |

| 5711  |                                 | Configuration          |                     | Set Socket KLEI ALI V L          |

| E9H   | EEPROM_ERASE                    |                        |                     | Erase EEPROM                     |

|       |                                 | EEPROM address (2)     |                     |                                  |

| EAH   | EEPROM_WRITE                    | Length                 |                     | Write EEPROM                     |

|       |                                 | Data flow (N)          |                     |                                  |

| EBH   | EEPROM READ                     | EEPROM address (2)     | Data flow (N)       | Read EEPROM                      |

|       |                                 | Length                 | Data flow (N)       | KCau EEF KOW                     |

| ECH   | READ_GPIO_REG                   | GPIP0 register address | GPI0 register value | Read GPIO register               |

| FDH   | WRITE GDIO REG                  | GPIP0 register address |                     | Write GPIO register              |

|       | EDH WRITE_GPIO_REG GPIP0 regist |                        |                     | white of 10 register             |

Commands in the shaded part of the table usually need to be executed for a certain period of time and the execution status of the command is queried. The MCU can obtain the status through GET\_CMD\_STATUS (refer to CH395INC.H for the definition of status).

## 5.1 CMD\_GET\_IC\_VER

This command is used to obtain the chip and firmware version, and the returned 1 byte data is the version number.

# 5.2 CMD\_SET\_BAUDRATE

This command is used to set the baud rate of serial communication of CH395. When CH395 works in serial communication mode, the default communication baud rate after reset is set by the level combination of SDO,

SDI and SCK pins (refer to Section 6.3 of this datasheet), and the default communication baud rate is 9600bps when these pins are suspended. If the MCU supports high communication speed, the baud rate of serial communication can be dynamically adjusted by this command. This command needs to input three data, namely baud rate coefficient 0, baud rate coefficient 1 and baud rate coefficient 2. The following table shows the corresponding relationship with baud rate.

Table 5-2 Baud rate

| Table 5-2 Daud Tale  |                         |                         |                                          |  |

|----------------------|-------------------------|-------------------------|------------------------------------------|--|

| Baud rate            | Baud rate               | Baud rate               | Serial port communication baud           |  |

| coefficient 2        | coefficient 1           | coefficient 0           | rate (bps)                               |  |

| 00H                  | 12H                     | СОН                     | 4800                                     |  |

| 00H                  | 25H                     | 80H                     | 9600                                     |  |

| 00H                  | 4BH                     | 00H                     | 19200                                    |  |

| 00H                  | 96H                     | 00H                     | 38400                                    |  |

| 00H                  | E1H                     | 00H                     | 57600                                    |  |

| 01H                  | 2CH                     | 00H                     | 76800                                    |  |

| 01H                  | С2Н                     | 00H                     | 115200                                   |  |

| 07H                  | 08H                     | 00H                     | 460800                                   |  |

| 0EH                  | 10H                     | 00H                     | 921600                                   |  |

| 0FH                  | 42H                     | 40H                     | 1M                                       |  |

| 1EH                  | 84H                     | 80H                     | 2M                                       |  |

| 4CH                  | 4BH                     | 40H                     | 5M                                       |  |

| 98H                  | 96H                     | 80H                     | 10M                                      |  |

| Calculation formula: |                         |                         |                                          |  |

| BaudRate = (Baud ra  | te coefficient 2<<16) - | + (Baud rate coefficien | nt $1 \le 8$ ) + Baud rate coefficient 0 |  |

Set the execution time of the serial communication baud rate configuration command by default to TE8 (the minimum is 1ms, see Table 7-4). After completion, CH395 will output the operating state at the new baud rate. The MCU needs to adjust its own baud rate as soon as possible within TE8 time and wait for CH395 to answer.

### 5.3 CMD\_ENTER\_SLEEP

This command causes the CH395 chip to enter a low-power sleep suspend state. Pull the CH395RXD pin down by 35us or above in serial port mode, and pull the SCS or PCS# chip select pin down by 35us or above in SPI or parallel port mode to remove the CH395 from the low power state. Therefore, after the MCU issues the CMD\_ENTER\_SLEEP command, the SCS or PCS# chip select should be invalid immediately.

The MAC and PHY that enter sleep state CH395 will enter power-down mode and disconnect the Ethernet connection.

After waking up from sleep mode, the CH395 takes about 4ms to complete the wake-up process. During this wake-up phase, CH395 will not parse or respond to any received command code. Therefore, do not send any command code to CH395 during CH395 being awakened. It is recommended that the user wake up for 4ms before operating on CH395.

## 5.4 CMD\_RESET\_ALL

This command causes CH395 to perform a hardware reset. Normally, hardware reset is completed within 15ms.

#### 5.5 CMD\_CHECK\_EXIST

This command is used to test the communication interface and working status to check whether the CH395 is working properly. This command requires input of 1 byte of data, which can be any data. If CH395 works normally, then the output data of CH395 is bitwise inverse of the input data. For example, if the input data is 57H, the output data is A8H.

### 5.6 CMD\_SET\_PHY

This command uses the connection method to set the CH395 Ethernet PHY. The default is automatic negotiation method. This command requires inputting 1 byte of data, which is the connection method code:

Disconnect PHY when connection mode code is 01H;

PHY is 10M full duplex when the connection mode code is 02H;

PHY is 10M half-duplex when the connection mode code is 04H;

PHY is 100M full-duplex When the connection mode code is 08H;

PHY is 100M half-duplex when the connection mode code is 10H;

PHY auto-negotiation when the connection mode code is 20H.

After receiving this command, CH395 will reset the MAC and PHY and reconnect according to the newly set connection mode. If Ethernet is connected, it will be disconnected and reconnected.

#### 5.7 CMD\_SET\_MAC\_ADDR

This command is used to set the MAC address of CH395. You need to enter a 6-byte MAC, and the low byte of the MAC address comes first. The CH395 chip will store the MAC address in the internal EEPROM. This command takes about 30us to complete.

The CH395 chip has been programmed with the MAC address assigned by IEEE when it leaves the factory. Please do not set the MAC address unless it is necessary.

#### 5.8 CMD\_SET\_IP\_ADDR

This command is used to set the IP address of CH395. You need to enter a 4-byte IP address, with the IP low byte first. In this manual, all commands containing IP input or output are in the byte order of IP low byte first, which will not be explained below.

#### 5.9 CMD\_SET\_GWIP\_ADDR

This command is used to set the gateway address of CH395. You need to enter a 4-byte IP address.

#### 5.10 CMD\_SET\_MASK\_ADDR

This command is used to set the subnet mask of CH395. This command requires a 4-byte mask. The default value is 255.255.255.0, which can be left unchecked.

#### 5.11 CMD SET MAC FILT

This command is used to set the MAC filtering mode. The MAC can set multiple filtering modes. This command needs to input 9 bytes of data, the first byte is filter mode, and the meaning of each bit of this data is as follows:

| Bit   | Name | Description |  |

|-------|------|-------------|--|

| [5:7] | -    | Reserved    |  |

| 4 | SEND_ENABLE   | Send enable               |

|---|---------------|---------------------------|

| 3 | RECV_ENABLE   | Receive enable            |

| 2 | RECV_MULTIPKT | Receive multicast packets |

| 1 | RECV_ALL      | Receive all data          |

| 0 | RECV_BROADPKT | Receive broadcast packet  |

The above bits are 1 for enable, and 0 for disable. After CH395 is reset, RECV\_BROADPKT, RECV\_ENABLE and SEND\_ENABLE are enabled by default.

The following table shows what you mean:

| <b>m</b> 1 1 |     | 1110    | 01. 1     |         |

|--------------|-----|---------|-----------|---------|

| Table        | 5-4 | MAC     | filtering | meaning |

| 10010        | • • | 1.11.10 |           |         |

| RECV_ENABLE | RECV_ALL | RECV_BROADPKT             | RECV_MULTIPKT             | Description                                                                                                                                     |

|-------------|----------|---------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | 0        | 0                         | 0                         | Receive packets matching the                                                                                                                    |

|             | -        | -                         | -                         | MAC address                                                                                                                                     |

| 1           | 1        | Х                         | Х                         | Receive all packets                                                                                                                             |

|             |          |                           |                           | Receive packets matching the                                                                                                                    |

| 1           | 0        | 1                         | 0                         | MAC address                                                                                                                                     |

|             |          |                           |                           | Receive broadcast packets                                                                                                                       |

|             |          |                           |                           | Receive packets matching the                                                                                                                    |

| 1           | 0        | 0 0                       | 1                         | MAC address                                                                                                                                     |

|             |          |                           |                           | Receive multicast packets                                                                                                                       |

|             |          |                           |                           | Receive packets matching the                                                                                                                    |

| 1           | 0        | 1                         | 1                         | Receive packets matching the   MAC address   Receive broadcast packets   Receive packets matching the   MAC address   Receive multicast packets |

|             | 1        |                           | Receive broadcast packets |                                                                                                                                                 |

|             |          | Receive multicast packets |                           |                                                                                                                                                 |

| 0           | Х        | X                         | Х                         | Prohibit receiving                                                                                                                              |

The 2nd to 5th bytes are HASH0 (Hash Table 0), and the 6th to 9th bytes are Hash H1 (Hash Table 1). HASH0 and Hash H1 are only valid when multicast is turned on.

HASH0 and HASH1 together form a 64-bit HASH table, with 0-31 bits being HASH0 and 32-63 bits being HASH1.

HASH table calculation method: calculate a 32-bit CRC value for the multicast address by using standard Ethernet redundancy check (CRC32), use the upper 6 bits of this CRC value as the index value, and write 1 to the corresponding bit of the HASH table. For example, if the upper 6 bits of the CRC value calculated by the multicast address are 32, the 0 th bit of HASH1 should be written as 1.

### 5.12 CMD\_GET\_PHY\_STATUS

This command is used to obtain the connection status of PHY. After receiving this command, CH395 will query the current connection status of PHY and output a 1-byte PHY connection status code:

A connection status code of 01H indicates that the PHY connection is disconnected;

A connection status code of 02H indicates that the PHY connection is 10M full-duplex;

A connection status code of 04H indicates that the PHY connection is 10M half-duplex;

A connection status code of 08H indicates that the PHY connection is 100M full-duplex;

A connection status code of 10H indicates that the PHY connection is 100M half-duplex.

## 5.13 CMD\_INIT\_CH395

This command is used to initialize CH395, including initializing the MAC, PHY and TCP/IP protocol stack of CH395. This command takes about 5ms to complete. MCU can send GET\_CMD\_STATUS to inquire whether the execution is completed and the execution status.

# 5.14 CMD\_GET\_UNREACH\_IPPORT

This command is used to obtain unreachable IP, port and protocol type. When an unreachable message is received, CH395 will generate an unreachable interrupt. MCU can use this command to obtain unreachable information. After receiving this command, CH395 will output 1-byte unreachable code, 1 byte protocol type, 2 bytes port number (low byte first) and 4 bytes IP in turn. MCU can judge whether the protocol is unreachable, the port is unreachable or the IP is unreachable according to the unreachable code. For unreachable codes, please refer to RFC792 (CH395INC.H defines four common unreachable codes).

# 5.15 CMD\_GET\_GLOB\_INT\_STATUS

This command is used to obtain the global interrupt status. After receiving this command, CH395 will output the global interrupt status of 1-byte. The global interrupt status is defined as follows:

| Bit | Name                 | Description                |  |  |  |

|-----|----------------------|----------------------------|--|--|--|

| 7   | GINT_STAT_SOCK3      | Socket3 interrupt          |  |  |  |

| 6   | GINT_STAT_SOCK2      | Socket2 interrupt          |  |  |  |

| 5   | GINT_STAT_SOCK1      | Socket1 interrupt          |  |  |  |

| 4   | GINT_STAT_SOCK0      | Socket0 interrupt          |  |  |  |

| 3   | GINT_STAT_DHCP       | DHCP interrupt             |  |  |  |

| 2   | GINT_STAT_PHY_CHANGE | PHY state change interrupt |  |  |  |

| 1   | GINT_STAT_IP_CONFLI  | IP conflict                |  |  |  |

| 0   | GINT_STAT_UNREACH    | Unreachable interrupt      |  |  |  |

Table 5-5 Global interrupt 1

- ① GINT\_STAT\_UNREACH: unreachable interrupt. When CH395 receives the ICMP unreachable interrupt message, it saves the IP address, port and protocol type of the unreachable IP packet in the unreachable information table, and then generates this interrupt. When the MCU receives this interrupt, it can send the GET\_UNREACH\_IPPORT command to obtain the unreachable information.

- ② Gint\_stat\_IP\_conf Li: IP conflict interrupt. This interrupt occurs when CH395 detects that its own IP address is the same as that of other network devices in the same network segment.

- ③ Gint\_stat\_phy\_change: PHY change is interrupted. This interrupt occurs when the PHY connection of CH395 changes, for example, the PHY state changes from the connected state to the disconnected state or from the disconnected state to the connected state. The MCU can send the GET\_PHY\_STATUS command to get the status of the current PHY connection.

- ④ Gint\_stat\_DHCP: DHCP interrupt. If the MCU enables the DHCP function of CH395, CH395 will generate this interrupt after DHCP succeeds or times out, and the MCU can send CMD\_GET\_DHCP\_STATUS command to obtain the DHCP status. If the status is 0, it means success, otherwise it means timeout failure.

- ⑤ Gint\_stat\_sock 0 ~ gint\_stat\_sock 3: socket interrupt. CH395 will generate this interrupt when there is an interrupt event in the Socket, and the MCU needs to send GET\_INT\_STATUS\_SN to get the interrupt status of the Socket. Please refer to the GET\_INT\_STATUS\_SN section.

After this command is executed, CH395 will set the INT# pin high and clear the global interrupt status.

### 5.16 CMD\_GET\_GLOB\_INT\_STATUS\_ALL

This command is used to obtain the global interrupt status. After receiving this command, CH395 will output the global interrupt status of 2 bytes. The global interrupt status is defined as follows:

| Bit     | Name                 | Description                |

|---------|----------------------|----------------------------|

| [12:15] | -                    | Reserved                   |

| 11      | GINT_STAT_SOCK7      | Socket7 interrupt          |

| 10      | GINT_STAT_SOCK6      | Socket6 interrupt          |

| 9       | GINT_STAT_SOCK5      | Socket5 interrupt          |

| 8       | GINT_STAT_SOCK4      | Socket4 interrupt          |

| 7       | GINT_STAT_SOCK3      | Socket3 interrupt          |

| 6       | GINT_STAT_SOCK2      | Socket2 interrupt          |

| 5       | GINT_STAT_SOCK1      | Socket1 interrupt          |

| 4       | GINT_STAT_SOCK0      | Socket0 interrupt          |

| 3       | GINT_STAT_DHCP       | DHCP interrupt             |

| 2       | GINT_STAT_PHY_CHANGE | PHY state change interrupt |

| 1       | GINT_STAT_IP_CONFLI  | IP conflict                |

| 0       | GINT_STAT_UNREACH    | Unreachable interrupt      |

| Table | 5-6 | Global | interrupt | 2 |

|-------|-----|--------|-----------|---|

|-------|-----|--------|-----------|---|

For bits 0-7, please refer to section 5.15.

Gint\_stat\_sock  $4 \sim \text{gint}_{\text{stat}_{\text{sock}}}$ ?: socket interrupt. CH395 will generate this interrupt when there is an interrupt event in the Socket, and the MCU needs to send GET\_INT\_STATUS\_SN to get the interrupt status of the Socket. Please refer to the GET\_INT\_STATUS\_SN section.