#

# CH32V203 Datasheet

V2.8

# Overview

CH32V series are industrial-grade general-purpose microcontrollers designed based on QingKe 32-bit RISC-V. The whole series of products into the hardware stack area, fast interrupt entry and other designs, compared to the standard greatly improved the interrupt response speed. CH32V203 is based on 32-bit RISC-V core design of industrial-grade enhanced low-power general-purpose microcontrollers, high-performance, in the product features support 144MHz main frequency zero-wait operation, equipped with V4B core, work and sleep power consumption significantly reduced year-on-year. CH32V203 series integrated dual USB interface, support USB Host and USB Device function, with CAN interface (2.0B active), dual OPA, 4 groups of USART, dual I2C, 12-bit ADC, 10-channel Touchkey and other rich peripheral resources.

# Features

- Core:

- QingKe 32-bit RISC-V core with multiple instruction set combinations

- Fast programmable interrupt controller + hardware interrupt stack

- Branch prediction, conflict handling mechanism

- Single cycle multiplication, hardware division, hardware FPU

- System main frequency 144MHz

- Memory:

- Available with up to 64KB volatile data storage area SRAM

- Available with 224KB program memory CodeFlash (zero-wait application area + non-zerowait data area)

- 28KB BootLoader

- 128B non-volatile system configuration memory

- 128B user-defined memory

#### • Power management and low-power

#### consumption:

- System power supply  $V_{DD}$ : 3.3V

- Independent power supply for GPIO unit  $V_{I\!/\!O}\!\!:$  3.3V

- Low-power mode: Sleep, Stop, Standby

- $V_{\text{BAT}}$  independently powers RTC and backup register

- Clock & Reset

- Built-in factory-trimmed 8MHz RC oscillator

- Built-in 40 KHz RC oscillator

- Built-in PLL, optional CPU clock up to 144MHz

- High-speed external 3~25MHz oscillator

- Low-speed external 32.768 KHz oscillator

- Power on/down reset, programmable voltage detector

- Real-time clock (RTC): 32-bit independent RTC timer

- 1 group of 8-channel general-purpose DMA controller

- 8 channels, support ring buffer

- Support TIMx/ADC /USART/I2C/SPI

- 2 groups of OPAs and comparators: connected with ADC and TIMx

- 2 groups of 12-bit ADC

- Analog input range: V<sub>SSA</sub>~V<sub>DDA</sub>

- 16 external signals + 2 internal signals

- On-chip temperature sensor

- Dual ADC conversion mode

- 16-channels Touch-Key detection

#### • Multiple timers

- 1×16-bit advanced-control timers, with dead zone control and emergency brake; can offer PWM complementary output for motor control

- 3×16-bit general-purpose timers, provide input capture/output comparison/PWM/pulse counting/incremental encoder input

- 1×32-bit general-purpose timer (for CH32V203RBx)

- 2 watchdog timers (independent watchdog and window watchdog)

- SysTick: 64-bit counter

- Communication interfaces:

- 4 USART interfaces

- 2 I2C interfaces (support SMBus/PMBus)

- 2 SPI interfaces

- USB2.0 full-speed device interface (full-speed and low-speed)

- USB2.0 full-speed host/device interface

- CAN interfaces (2.0B active)

- Fast GPIO port

- 37 I/O ports, mapping 16 external interrupts

- Security features: CRC unit, 96-bit unique ID

- Debug mode: 2-wire serial debug interface (SDI)

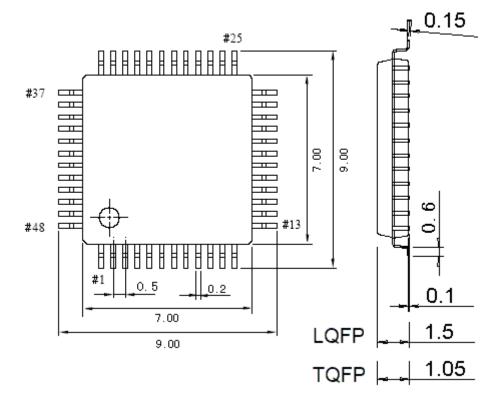

- Package: LQFP, QFN, TSSOP or QSOP

# **Chapter 1 Series Product Description**

CH32V series are industrial-grade general-purpose enhanced MCUs based on 32-bit RISC-V instruction set and architecture. Its products are divided by function resources into categories such as general-purpose, connectivity, and wireless communication. They extend each other in terms of package types, peripheral resources and quantities, pin numbers, and device characteristics, but they are compatible with each other in software, functions, and hardware pin configurations. The product iterations and rapid applications provide freedom and convenience for users in product development.

For the features of this series of products, please refer to the datasheet.

For the peripheral function description, usage and register configuration, please refer to "CH32FV2\_V3RM".

The datasheets and reference manuals can be downloaded on the official website of WCH: https://www.wch-ic.com/

Information about the RISC-V instruction set architecture can be downloaded from: https://riscv.org/

This manual is for CH32V203 series datasheet. Please refer to "CH32V307DS0" for V303/305/307/317 series and "CH32V208DS0" for V208 series.

| Small-and-medium capacit                                                                                 | Small-and-medium capacity general-purpose (V203)                                                            |                                                                                                                                                       |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| QingKe                                                                                                   | e V4B                                                                                                       | QingKe V4C                                                                                                                                            |  |  |  |  |  |  |  |  |

| 32K FLASH                                                                                                | 64K FLASH                                                                                                   | 128K FLASH                                                                                                                                            |  |  |  |  |  |  |  |  |

| 10K SRAM                                                                                                 | 20K SRAM                                                                                                    | 64K SRAM                                                                                                                                              |  |  |  |  |  |  |  |  |

| 2*ADC (TKey)<br>ADTM<br>3*GPTM<br>2*USART<br>SPI<br>I2C<br>USBD<br>USBFS<br>CAN<br>RTC<br>2*WDG<br>2*OPA | 2*ADC(TKey)<br>ADTM<br>3*GPTM<br>4*USART<br>2*SPI<br>2*I2C<br>USBD<br>USBFS<br>CAN<br>RTC<br>2*WDG<br>2*OPA | ADC(TKey)<br>ADTM<br>3*GPTM<br>GPTM(32)<br>4*USART/UART<br>2*SPI<br>2*I2C<br>USBD<br>USBFS<br>CAN<br>RTC<br>2*WDG<br>2*OPA<br>ETH-10M(+PHY)<br>BLE5.3 |  |  |  |  |  |  |  |  |

Table 1-1-1 CH32V203/208 Series overview

Note: The number of peripherals or functions of some products in the same category may be limited by the package, please confirm the product package when selecting.

| Large-capacity                                                                                                   | y general-purpose                                                                                                                                               | Conne                                                                                                                                                                     | ectivity                                                                                                                                                          | Interconnectivity                                                                                                                                                                                                       | Interconnectivity                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7)                                                                                                               | /303)                                                                                                                                                           | (V3                                                                                                                                                                       | 305)                                                                                                                                                              | (V307)                                                                                                                                                                                                                  | (V317)                                                                                                                                                                                                                       |

|                                                                                                                  |                                                                                                                                                                 | Qing                                                                                                                                                                      | Ke V4F                                                                                                                                                            |                                                                                                                                                                                                                         |                                                                                                                                                                                                                              |

| 128K Flash                                                                                                       | 256K Flash                                                                                                                                                      | 128K Flash                                                                                                                                                                | 256K Flash                                                                                                                                                        | 256K Flash                                                                                                                                                                                                              | 256K Flash                                                                                                                                                                                                                   |

| 32K SRAM                                                                                                         | 64K SRAM                                                                                                                                                        | 32K SRAM                                                                                                                                                                  | 64K SRAM                                                                                                                                                          | 64K SRAM                                                                                                                                                                                                                | 64K SRAM                                                                                                                                                                                                                     |

| 2*ADC(TKey<br>)<br>2*DAC<br>ADTM<br>3*GPTM<br>3*USART<br>2*SPI<br>2*I2C<br>USBFS<br>CAN<br>RTC<br>2*WDG<br>4*OPA | 2*ADC(TKey)<br>2*DAC<br>4*ADTM<br>4*GPTM<br>2*BCTM<br>8*USART/UAR<br>T<br>3*SPI(2*I2S)<br>2*I2C<br>USBFS<br>CAN<br>RTC<br>2*WDG<br>4*OPA<br>RNG<br>SDIO<br>FSMC | 2*ADC(TKey)<br>2*DAC<br>4*ADTM<br>4*GPTM<br>2*BCTM<br>5*USART/UAR<br>T<br>3*SPI(2*I2S)<br>2*I2C<br>OTG_FS<br>USBHS(+PHY)<br>2*CAN<br>RTC<br>2*WDG<br>4*OPA<br>RNG<br>SDIO | 2*ADC(TKey)<br>2*DAC<br>4*ADTM<br>4*GPTM<br>2*BCTM<br>5*USART/UAR<br>T<br>3*SPI(2*I2S)<br>2*I2C<br>OTG_FS<br>USBHS(+PHY)<br>2*CAN<br>RTC<br>2*WDG<br>4*OPA<br>RNG | 2*ADC(TKey)<br>2*DAC<br>4*ADTM<br>4*GPTM<br>2*BCTM<br>8*USART/UAR<br>T<br>3*SPI(2*I2S)<br>2*I2C<br>OTG_FS<br>USBHS(+PHY)<br>2*CAN<br>RTC<br>2*WDG<br>4*OPA<br>RNG<br>SDIO<br>FSMC<br>DVP<br>ETH-1000M<br>MAC<br>10M PHY | 2*ADC(TKey)<br>2*DAC<br>4*ADTM<br>4*GPTM<br>2*BCTM<br>8*USART/UAR<br>T<br>3*SPI(2*I2S)<br>2*I2C<br>OTG_FS<br>USBHS(+PHY)<br>2*CAN<br>RTC<br>2*WDG<br>4*OPA<br>RNG<br>SDIO<br>FSMC<br>DVP<br>ETH-1000M<br>MAC<br>10M/100M PHY |

#### Table 1-1-2 CH32V303/305/307/317 Series overview

*Note: The number of peripherals or functions of some products in the same category may be limited by the package, please confirm the product package when selecting.*

Abbreviations: ADTM: Advanced-control Timer GPTM: General-purpose Timer GPTM(32): 32-bit General-purpose Timer BCTM: Basic Timer TKey: Touch key OPA: Operational Amplifier/Comparator

RNG: Random Number Generator USBD: Universal Serial Bus Full-speed Device USBFS: Universal Serial Bus Full-speed Host/Device USBHS: Universal Serial Bus High-speed Host/Device

| Feature Ins | struction<br>Set |  | Interrupt<br>Nesting<br>Level | Number of<br>Fast<br>Interrupt | Integer<br>Division<br>Period | Vector table<br>mode | Extended instruction | 2 |

|-------------|------------------|--|-------------------------------|--------------------------------|-------------------------------|----------------------|----------------------|---|

|-------------|------------------|--|-------------------------------|--------------------------------|-------------------------------|----------------------|----------------------|---|

#### Table 1-2 Overview of Cores

|     |       |   |   | Channels |   |                        |         |          |

|-----|-------|---|---|----------|---|------------------------|---------|----------|

| V4B | IMAC  | 2 | 2 | 4        | 9 | Address or instruction | Support | No       |

| V4C | IMAC  | 2 | 2 | 4        | 5 | Address or instruction | Support | Standard |

| V4F | IMAFC | 3 | 8 | 4        | 5 | Address or instruction | Support | Standard |

*Note:* For information about the core, please refer to the QingKeV4 microprocessor manual "QingKeV4\_Processor\_Manual".

# **Chapter 2 Specification**

CH32V203 series are 32-bit RISC core MCUs based on the RISC-V instruction set architecture (ISA), with 144MHz operating frequency, and built-in high-speed memory. It has multiple buses working synchronously, and provides a wealth of peripheral functions and enhanced I/O ports. This series of products has built-in 2 12-bit ADC modules, multiple timers, multi-channel capacitance touch key detection (TKey) and other functions. It also contains standard and dedicated communication interfaces: I<sup>2</sup>C, SPI, USART, CAN controller, USB2.0 full-speed host/device controller, etc.

The rated working voltage of the product is 3.3V, and the working temperature range is  $-40^{\circ}C \sim 85^{\circ}C$  in industrial grade. It supports several power-saving operating modes to meet the product's low-power application requirements. Various models in the series are different in terms of resource allocation, number of peripherals, peripheral functions, etc., and can be selected as needed.

## 2.1 Model Comparison

Table 2-1 Low-and-medium-density general-purpose products resource allocation

|                         |                                       | Part No. |            |    |        |      | CH32 |       |      |     |     |                     |

|-------------------------|---------------------------------------|----------|------------|----|--------|------|------|-------|------|-----|-----|---------------------|

| Differ                  | ences                                 |          | F6         | F  | 8      | G6   | G8   | K6    | K8   | C6  | C8  | RB                  |

|                         | Pin count                             | t        | 20         | 20 | 0      | 28   | 28   | 32    | 32   | 48  | 48  | 64                  |

|                         | Flash (bytes                          | ) (1)    | 32K        | 64 | K      | 32K  | 64K  | 32K   | 64K  | 32K | 64K | 128K <sup>(2)</sup> |

|                         | SRAM (byt                             | es)      | 10K        | 20 | K      | 10K  | 20K  | 10K   | 20K  | 10K | 20K | 64K                 |

|                         | GPIO port co                          | ount     | 16         | 1′ | 7      | 24   | 24   | 26    | 26   | 37  | 37  | 51                  |

|                         | Advanced<br>(16-b                     |          | 1(3)       | 10 | 3)     | 1(3) | 1(3) | 1     | 1    | 1   | 1   | 1                   |

|                         | General-purpose<br>(16-bit)           |          | 3(3)       | 3( | 3)     | 3(3) | 3(3) | 3     | 3    | 3   | 3   | 3                   |

| Timer                   | · · · · · · · · · · · · · · · · · · · |          |            | -  |        |      |      |       |      |     |     | 1                   |

|                         | Watchdog                              |          |            |    |        | 2 (  | WWDG | + IWI | DG)  |     |     |                     |

|                         | SysTick                               |          | auma ata d |    |        |      |      |       |      |     |     |                     |

|                         | (64-b                                 | oit)     | supported  |    |        |      |      |       |      |     |     |                     |

|                         | RTC                                   |          | supported  |    |        |      |      |       |      |     |     |                     |

| ADC                     | C/TKey (chan<br>count)                | nel@unit | 9@2        |    |        |      |      | 10@2  | 16@1 |     |     |                     |

|                         | OPA                                   |          | 1          | 2  | l<br>K | 2    | 2    | 2     | 2    | 2   | 2   | 2                   |

| J                       | USART/                                | UART     | 1          | 2  | ,      | 2    | 2    | 2     | 2    | 2   | 4   | 4                   |

| rfac                    | SP                                    | [        | 1          | 1  |        | 1    | 1    | 1     | 1    | 1   | 2   | 2                   |

| inte                    | I2C                                   | 2        | 0          | 1  | -      | 1    | 1    | 1     | 1    | 1   | 2   | 2                   |

| ation                   | CA                                    | N        | 1          | -  |        | 1    | 1    | 1     | 1    | 1   | 1   | 1                   |

| Junic                   | USB                                   | USBD     | 1          | -  | 1      | 1    | 1    | 1     | 1    | 1   | 1   | 1                   |

| Communication interface | (FS)                                  | USBHD    | -          | 1  | -      | -    | 1    | -     | -    | 1   | 1   | 1                   |

|                         | Ether                                 | net      |            |    |        |      | -    |       |      |     |     | 10M                 |

| Part No.              | CH32V203                     |             |       |       |        |    |      |        |               |         |

|-----------------------|------------------------------|-------------|-------|-------|--------|----|------|--------|---------------|---------|

| Differences           | F6                           | F           | 8     | G6    | G8     | K6 | K8   | C6     | C8            | RB      |

| CPU clock speed       | Max: 144MHz                  |             |       |       |        |    |      |        |               |         |

| Rated voltage         | 3.3V                         |             |       |       |        |    |      |        |               |         |

| Operating temperature | Industrial-grade: -40°C~85°C |             |       |       |        |    |      |        |               |         |

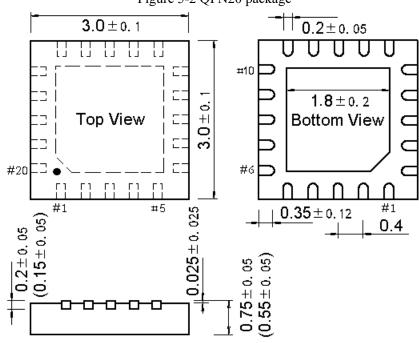

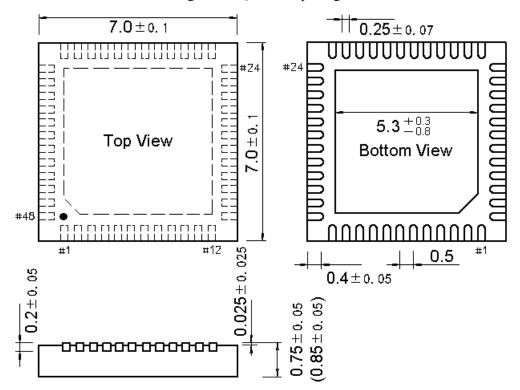

| Package               | TSSOP20,<br>QFN20            | TSSOP2<br>0 | QFN20 | QFN28 | QSOP28 | LQ | FP32 | LQFP48 | LQFP<br>QFN48 | LQFP64M |

|                         |                             | Part No.  |         |             |           |           | CH32V            | /203      |      |                |                     |  |

|-------------------------|-----------------------------|-----------|---------|-------------|-----------|-----------|------------------|-----------|------|----------------|---------------------|--|

| Differer                | nces                        |           | F6      | F           | 78        | G6        | G8               | K8        | C6   | C8             | RB                  |  |

|                         | Pin count                   |           | 20      | 2           | 20        | 28        | 28               | 32        | 48   | 48             | 64                  |  |

| F                       | lash (bytes)                | (1)       | 32K     | 64          | 4K        | 32K       | 64K              | 64K       | 32K  | 64K            | 128K <sup>(2)</sup> |  |

| S                       | SRAM (byte                  | s)        | 10K     | 20          | )K        | 10K       | 20K              | 20K       | 10K  | 20K            | 64K                 |  |

| G                       | PIO port co                 | unt       | 16      | 1           | 7         | 24        | 24               | 26        | 37   | 37             | 51                  |  |

|                         | Advanced<br>(16-b           |           | 1(3)    | 1           | (3)       | 1(3)      | 1 <sup>(3)</sup> | 1         | 1    | 1              | 1                   |  |

|                         | General-purpose<br>(16-bit) |           | 3(3)    | 3           | (3)       | 3         | 3                | 3         | 3    | 3              | 3                   |  |

| Timer                   | General-p<br>(32-b          | -         |         |             |           |           | -                |           |      |                | 1                   |  |

|                         | Watch                       | dog       |         |             |           | 2 ( V     | WWDG ·           | + IWDG )  | )    |                |                     |  |

|                         | SysT                        | ick       |         | Supported   |           |           |                  |           |      |                |                     |  |

|                         | (64-b                       | oit)      |         |             |           |           |                  |           |      |                |                     |  |

|                         | RTC                         |           |         | 1           |           |           | Suppo            | rted      |      |                |                     |  |

| ADC/T                   | Key (chann count)           | el@unit   | 9@2 9@2 |             | 10@2      | 10@2      | 10@2             | 10@2      | 10@2 | 16@1           |                     |  |

|                         | OPA                         |           | 1 2     |             | 2         | 2         | 2                | 2         | 2    | 2              |                     |  |

|                         | USART/                      | UART      | 1       |             | 2         | 2         | 2                | 2         | 2    | 4              | 4                   |  |

| face                    | SP                          | [         | 1       |             | 1         | 1         | 1                | 1         | 1    | 2              | 2                   |  |

| nter                    | I2C                         | 2         | -       | 1           | -         | 1         | 1                | 1         | 1    | 2              | 2                   |  |

| ioni                    | CA                          | N         | 1       |             | -         | 1         | 1                | 1         | 1    | 1              | 1                   |  |

| micat                   | USB                         | USBD      | 1       | -           | 1         | 1         | 1                | 1         | 1    | 1              | 1                   |  |

| Communication interface | (FS)                        | USBH<br>D | -       | 1           | -         | -         | 1                | -         | 1    | 1              | 1                   |  |

|                         | Ether                       | net       |         |             |           |           | -                |           |      |                | 10M                 |  |

| C                       | PU clock sp                 | eed       |         |             |           | N         | Max: 14          | 4MHz      |      |                |                     |  |

|                         | Rated voltage               |           |         |             |           |           | 3.3              | V         |      |                |                     |  |

| Oper                    | Operating temperature       |           |         |             |           | Industria | al-grade         | : -40°C~8 | 5°C  |                |                     |  |

|                         | Package                     |           | TSSOP20 | TSSO<br>P20 | QFN2<br>0 | QFN2<br>8 | QSOP<br>28       | LQFP32    | -    | FP48,<br>148X7 | LQFP64M             |  |

Note: 1. Flash bytes represent zero-wait run area  $R_{0WAIT}$ . For the V203 series, non-zero-wait area is (224K- $R_{0WAIT}$ ).

2. 128K FLASH+64K SRAM products support user-selected word configuration as one of several combinations (128K FLASH+64K SRAM), (144K FLASH+48K SRAM), (160K FLASH+32K SRAM).

3. Timer PWM, capture and other functions involving pin signals need to be combined with the actual chip package pins, some package chips do not lead to such functions cannot be used.

## 2.2 System Architecture

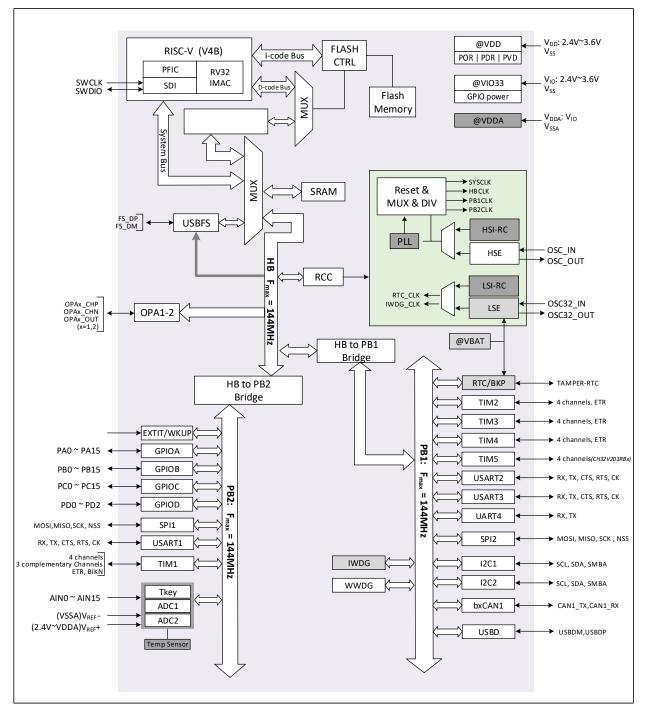

The microcontroller is based on the RISC-V instruction set architecture (ISA) in which the core, arbitration unit, DMA module, SRAM storage and other parts are interacted through multiple sets of buses. A general-purpose DMA controller is integrated in the chip to reduce the burden on the CPU and improve access efficiency. The application of a multi-level clock management mechanism reduces the operating power consumption of peripherals. At the same time, it has a data protection mechanism and measures such as automatic clock switching protection to increase system stability. The following figure is a block diagram of the overall internal structure of the series of products.

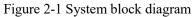

## 2.3 Memory Map

Figure 2-2 Memory address map

## 2.4 Clock Tree

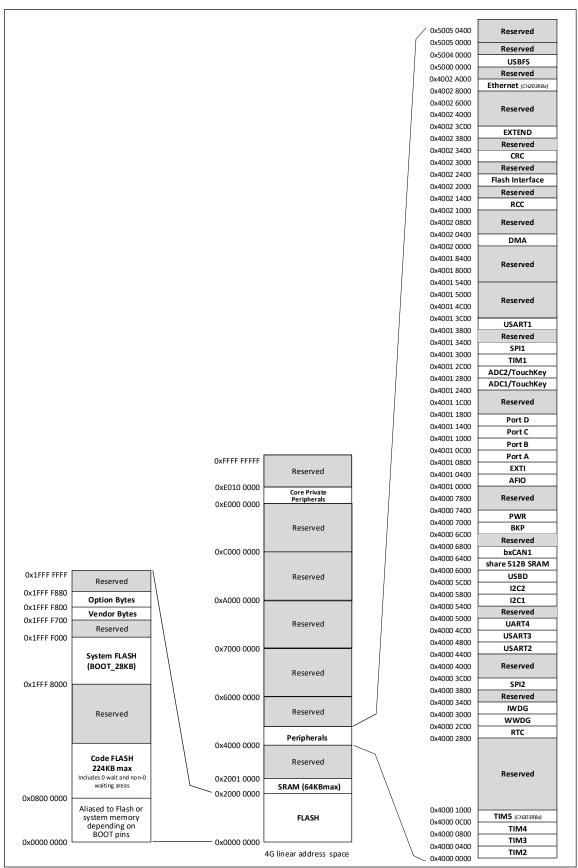

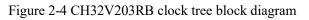

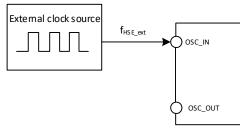

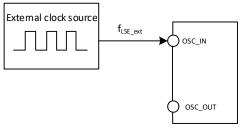

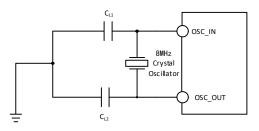

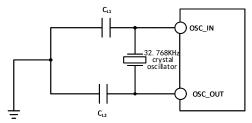

Four groups of clock sources are introduced into the system: internal high-frequency RC oscillator (HSI), internal low-frequency RC oscillator (LSI), external high-frequency oscillator (HSE), and external low-frequency oscillator (LSE). Among them, the low-frequency clock source provides the clock reference for RTC and independent watchdog. The high-frequency clock source is directly or indirectly multiplied by the PLL and output as the system clock (SYSCLK). The system clock is then provided by each prescaler to provide the HB domain, PB1 domain, PB2 domain peripheral control clock and sampling or output clock. Some modules need to be directly provided by the PLL clock.

#### Figure 2-3 CH32V203 clock tree block diagram

Note: 1. When using the USB function, the CPU frequency must be 48MHz or 96MHz or 144MHz. when the system wakes up from downtime or standby, the system will automatically switch to HSI as the main frequency.

Note: 1. For CH32V203RB, the external crystal or clock (HSE) is 32M. When the external crystal is enabled, no load capacitor is required as it is built in.

2. The blue dotted line in Figure 2-4 above applies only to CH32V203RB chips with a lot number whose penultimate fifth digit is greater than zero.

## **2.5 Functional Description**

#### 2.5.1 RISC-V4B Processor

RISC-V4B supports the IMAC subset of the RISC-V instruction set. The processor is managed internally in a modular fashion and contains units such as fast programmable interrupt controller (PFIC), memory protection, branch prediction mode, and extended instruction support. Externally multiple buses are connected to external unit modules to enable interaction between external function modules and the core.

The processor can be flexibly applied in different scenarios, such as small-area low-power embedded scenarios, high-performance application operating system scenarios, etc., due to its minimal instruction set, multiple working modes, and modular customization extensions.

- Support machine and user privilege mode

- Fast Programmable Interrupt Controller (FPIC)

- Multi-level hardware interrupt stack

- Serial 2-wire debug interface

- Standard memory protection design

- Static or dynamic branch prediction, efficient jump, conflict detection

- Custom extended instructions

#### 2.5.2 On-chip Memory and Boot Mode

Up to 128K bytes of built-in SRAM area, used to store data, data will be lost after power failure. The specific capacity depends on the corresponding chip model.

Up to 480K bytes of built-in program Flash memory (Code FLASH), used for user application and constant data storage, including zero-wait program run area and non-zero-wait area. The specific size depends on the corresponding chip model.

Built-in 28K byte system memory (System FLASH), used for system boot program storage (manufacturer curing boot loader).

128 bytes are used for system non-volatile configuration word storage, and 128 bytes are used for user selection word storage.

At startup, one of 3 boot modes can be selected through the boot pins (BOOT0 and BOOT1):

- Boot from program flash

- Boot from system memory

- Boot from internal SRAM

The bootloader is stored in the system memory, and the contents of the program Flash memory storage can be reprogrammed through the USART1 and USB interface.

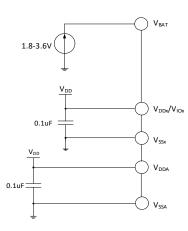

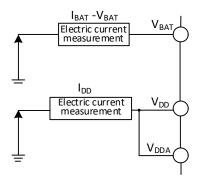

#### 2.5.3 Power Supply Scheme

- $V_{DD} = 2.4 \sim 3.6$ V: Power supply for some I/O pins and internal voltage regulator.

- $V_{I/O} = 2.4 \sim 3.6V$ : It supplies power to most of the I/O pins and the Ethernet module, which determines the pin output high voltage amplitude. Normal work during operation, the V<sub>IO</sub> voltage cannot be higher than the V<sub>DD</sub> voltage.

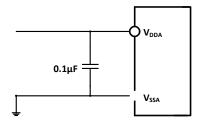

- $V_{DDA} = 2.4 \sim 3.6V$ : It supplies power to the analog part of the high-frequency RC oscillator, ADC, temperature sensor, DAC and PLL. The  $V_{DDA}$  voltage must be the same as the  $V_{I/O}$  voltage (If  $V_{DD}$  is

powered down and  $V_{I/O}$  is live, Then  $V_{DDA}$  must be live and consistent with  $V_{I/O}$ ). When using ADC,  $V_{DDA}$  must not be less than 2.4V.

•  $V_{BAT} = 1.8 \sim 3.6 V$ : Optional backup power supply. When  $V_{DD}$  is turned off, (through the internal power switch) independently powers the RTC, external low-frequency oscillator and backup registers.

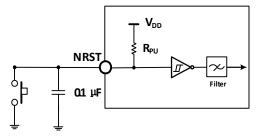

#### 2.5.4 Power Supply Monitor

This product integrates a power-on reset (POR)/power-down reset (PDR) circuit, which is always in working condition to ensure that the system is in supply. It works when the power exceeds 2.4V; when  $V_{DD}$  is lower than the set threshold ( $V_{POR/PDR}$ ), the device is placed in the reset state without using an external reset circuit.

In addition, the system is equipped with a programmable voltage monitor (PVD), which needs to be turned on by software to compare the voltage of  $V_{DD}$  power supply with the set threshold  $V_{PVD}$ .

Turn on the corresponding edge interrupt of PVD, and you can receive interrupt notification when  $V_{DD}$  drops to the PVD threshold or rises to the PVD threshold. Refer to Chapter 4 for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

#### 2.5.5 Voltage Regulator

After reset, the regulator is automatically turned on, and there are 3 operation modes according to the application mode.

- ON mode: normal operation, providing stable core power.

- Low-power mode: When the CPU enters Stop mode, the regulator can be selected to run with low- power consumption.

- OFF mode: When the CPU enters Standby mode, it automatically switches the regulator to this mode, the voltage regulator output is in high impedance, and the core power.

The voltage regulator is always ON after reset. It is OFF in Standby mode, and the regulator output is in high impedance.

#### 2.5.6 Low-power Mode

The system supports 3 low-power modes, which can be selected for low-power consumption, short start-up time and multiple wake-up events to achieve the best balance.

• Sleep mode

In Sleep mode, only the CPU clock is stopped, but all peripheral clocks are powered normally and the peripherals are in a working state. This mode is the shallowest low-power mode, but it is the fastest mode to wake-up the system.

Exit condition: any interrupt or wake-up event.

• Stop mode

In this mode, the FLASH enters low-power mode, and the PLL, HSI RC oscillator and HSE crystal oscillator are turned off. In the case of keeping the contents of SRAM and registers not lost, the Stop mode can achieve the lowest power consumption.

Exit conditions: any external interrupt/event (EXTI signal), external reset signal on NRST, IWDG reset, among which EXTI signal includes one of 16 external I/O ports, PVD output, RTC alarm clock, Ethernet wake-up signal or USB wake-up signal.

• Standby mode

In this mode, the main LDO of the system is turned off, the low-power LDO supplies power to the wake-up

circuit, all other digital circuits are powered off, and the FLASH is powered off. The system wakes up from Standby mode will generate a reset, and SBF (PWR\_CSR) will be set at the same time. After waking up, check the SBF status to know the low-power mode before waking up. SBF is cleared by the CSBF (PWR\_CR) bit. In the Standby mode, the contents of 32KB of SRAM can be kept (depending on the planning and configuration before going to bed), and the contents of the backup registers are kept.

Exit conditions: any external interrupt/event (EXTI signal), external reset signal on NRST, IWDG reset, a rising edge on the WKUP pin, where EXTI signal includes one of 16 external I/O ports, RTC alarm clock, Ethernet Wake-up signal, USB.

#### 2.5.7 CRC (cyclic redundancy check) Calculation Unit

The CRC (cyclic redundancy check) calculation unit uses a fixed polynomial generator to generate a CRC code from a 32-bit data word. In many applications, CRC-based technology is used to verify the consistency of data transmission or storage. Within the scope of the EN/IEC 60335-1 standard, a means of detecting flash errors is provided. The CRC calculation unit can be used to calculate the signature of the software in real time and compare it with the signature generated when the software is linked and generated.

#### 2.5.8 Programmable Fast Interrupt controller (PFIC)

The product has a built-in Programmable Fast Interrupt Controller (PFIC), which supports up to 255 interrupt vectors, and provides flexible interrupt management functions with minimal interrupt latency. The current product manages 8 core private interrupts and 88 peripheral interrupt management, and other interrupt sources are reserved. FPIC registers can be accessed in user and machine privileged modes.

- 2 individual maskable interrupts

- A non-maskable interrupt NMI

- Support hardware interrupt stack (HPE) without instruction overhead

- 4-channel vector table free interrupts (VTF)

- Vector table supports address or command mode

- Configurable interrupt nesting depth, up to 2 levels

- Support interrupt tail-chaining

#### 2.5.9 External Interrupt/Event Controller (EXTI)

The external interrupt/event controller contains a total of 19 edge detectors for generating interrupt/event requests. Each interrupt line can independently configure its trigger event (rising edge or falling edge or both edges), and can be individually masked; the suspend register maintains all interrupt request states. EXTI can detect that the pulse width is smaller than the clock period of the internal PB2. Up to 37 general-purpose I/O ports can be connected to 16 external interrupt lines.

#### 2.5.10 General DMA Controller

The system has built-in 2 groups of general-purpose DMA controllers, manages 18 channels in total, and flexibly handles high-speed data transmission from memory to memory, peripherals to memory, and memory to peripherals, and supports ring buffer mode. Each channel has a dedicated hardware DMA request logic to support one or more peripherals' access requests to the memory. The access priority, transfer length, source address and destination address of the transfer can be configured.

The main peripherals used by DMA include: general/advanced TIMx, ADC, USART, I<sup>2</sup>C and SPI.

Note: DMA and CPU access the system SRAM after arbitration by the arbiter.

#### 2.5.11 Clock and Boot

The system clock source HSI is turned on by default. After the clock is not configured or reset, the internal 8MHz RC oscillator is used as the default CPU clock, and then an external 3~25MHz clock or PLL clock can be additionally selected. When the clock security mode is turned on, if the HSE is used as the system clock (directly or indirectly), the system clock will automatically switch to the internal RC oscillator when the external clock is detected to be invalid, and the HSE and PLL will be automatically turned off at the same time; in low-power consumption mode, the system will automatically switch to the internal RC oscillator after waking up. If the clock interrupt is enabled, the software can receive the corresponding interrupt.

Multiple prescalers are used to configure the frequency of HB. The high-speed PB (PB2) and low-speed PB (PB1) regions provide peripheral clocks with a maximum frequency of 144MHz. Refer to the clock tree block diagram in Figure 2-3.

#### 2.5.12 Real Time Clock (RTC) and Backup Registers

The RTC and the backup register are in the backup power supply area inside the system. When  $V_{DD}$  is valid, it is powered by  $V_{DD}$ , and when  $V_{DD}$  is invalid, the internal power is automatically switched to the  $V_{BAT}$  pin.

RTC is a set of 32-bit programmable counters, and its time base supports 20-bit prescaler, which is used for longtime measurement. The clock reference comes from high-speed external clock (HSE) frequency division (please refer to the description of RTCSEL[1:0] in RCC\_BDCTLR register in Chapter 3.4.9 of CH32FV2x\_V3xRM manual for the frequency division coefficient of corresponding chips), external crystal low-frequency oscillator (LSE) or internal low-power RC oscillator (LSI). The LSE also has a backup power supply area, so when the LSE is selected as the RTC time base, the setting and time of RTC can remain unchanged after the system is reset or awakened from standby mode.

The backup register contains up to 42 16-bit registers, which can be used to store 84 bytes of user application data. This data can continue to be maintained after wake-up from Standby, or system Reset or power Reset. When the intrusion detection function is turned on, once the intrusion detection signal is valid, all contents in the backup register will be cleared.

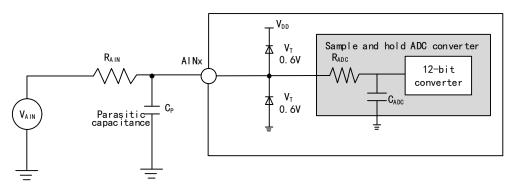

#### 2.5.13 Analog-to-digital Converter (ADC) and Touch-key Capacitance Detection (TKey)

The product is embedded with 2 12-bit analog/digital converters (ADC), sharing up to 16 external channels and 2 internal channels for sampling. The programmable channel sampling time can realize single, continuous, scanning or discontinuous conversion. And supports dual ADC conversion mode. The analog watchdog function is provided to allow very precise monitoring of one or more selected channels for monitoring the signal voltage of the channel. It supports external event-triggered conversion, the trigger source includes the internal signal and external pin of the on-chip timer; it also supports the use of DMA operations.

ADC internal channel sampling includes 1 channel of built-in temperature sensor sampling and 1 channel of internal reference power sampling. The temperature sensor generates a voltage that varies linearly with temperature. The temperature sensor is internally connected to the IN16 input channel, which is used to convert the output of the sensor to a digital value.

The capacitance touch key detection unit provides up to 16 detection channels, multiplexing the external channels of the ADC module. The detection result is converted and output by the ADC module, and the state of the touch key is recognized by the user software.

#### 2.5.14 Timer and Watchdog

The timers in the system include advanced timers, general timers, basic timers, watchdog timers, and system time base timers. The number of timers included in different products in the series is different, please refer to Table 2-2 for details.

| Timer                         |                                             | Resolution         | Count<br>Type         | Time Base                                                 | DMA              | Function                                                                                           |  |  |

|-------------------------------|---------------------------------------------|--------------------|-----------------------|-----------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------|--|--|

| Advanced-<br>control<br>timer | TIM1                                        | 16 bits            | Up<br>Down<br>Up/down | PB2 time<br>domain<br>16-bit divider                      | Supported        | PWM complementary output,<br>single pulse output<br>Input capture<br>Output compare<br>Timer count |  |  |

| General-<br>purpose<br>timer  | TIM2<br>TIM3<br>TIM4<br>TIM5 <sup>(1)</sup> | 16 bits<br>32 bits | Up<br>Down<br>Up/down | PB1 time<br>domain<br>16-bit divider                      | Supported        | Input capture<br>Output compare<br>Timer count                                                     |  |  |

| Window watchdog               |                                             | 7 bits             | Down                  | PB1 time<br>domain<br>4 types of<br>frequency<br>division | Not<br>supported | Timing<br>Reset the system (normal work)                                                           |  |  |

| Indepe<br>watch               |                                             | 12 bits            | Down                  | PB1 time<br>domain<br>7 types of<br>frequency<br>division | Not<br>supported | Timing<br>Reset the system (normal work +<br>low-power work)                                       |  |  |

| SysTic                        | k Timer                                     | 64 bits            | Up/down               | SYSCLK or<br>SYSCLK/8                                     | Not<br>supported | Timing                                                                                             |  |  |

| Table | 2-2 | Timer | comparison |

|-------|-----|-------|------------|

| Table | 2-2 | Immer | comparison |

Note 1: Applicable to CH32V203RBx.

#### • Advanced control timer

The advanced control timer is a 16-bit auto-loading up/down counter with a 16-bit programmable prescaler. In addition to the complete general-purpose timer function, it can be regarded as a three-phase PWM generator distributed to 6 channels, with a complementary PWM output function with dead zone insertion, allowing the timer to be updated after a specified number of counter cycles to repeat counting cycle, braking function, etc. Many functions of the advanced control timer are the same as the general timer, and the internal structure is also the same. Therefore, the advanced control timer can cooperate with other TIM timers through the timer link function to provide synchronization or event link functions.

#### • General-purpose timer

The general timer is a 16-bit or 32-bit auto-loading up/down counter with a programmable 16-bit prescaler and 4 independent channels. Each channel supports input capture, output comparison, and PWM generation and single pulse mode output. It can also work with advanced control timers through the timer link function to

provide synchronization or event link functions. In Debug mode, the counter can be frozen while the PWM outputs are disabled, thereby cutting off the switches controlled by these outputs. Any general-purpose timer can be used to generate PWM output. Each timer has an independent DMA request mechanism. These timers can also process signals from incremental encoders, as well as digital outputs from 1 to 3 Hall sensors.

#### • Independent watchdog

The independent watchdog is a configurable 12-bit down counter that supports 7 frequency division factors. The clock is provided by an internal independent 40 KHz RC oscillator (LSI); because the LSI is independent of the main clock, it can run in Stop and Standby modes. IWDG is outside the main program and can work completely independently. Therefore, it is used to reset the entire system when a problem occurs, or as a free time to provide timeout management for the application. It can be configured as software or hardware to start the watchdog through the option byte. In Debug mode, the counter can be frozen.

#### • Window Watchdog

The window watchdog is a 7-bit down counter and can be set to free-running. It can be used to reset the entire system when a problem occurs. It is driven by the main clock and has an early warning interrupt function; in Debug mode, the counter can be frozen.

#### • SysTick Timer

QingKe microprocessor core comes with a 64-bit optional incremental or decremental counter for generating SYSTICK exceptions (exception number: 15), which can be used exclusively in real-time operating systems to provide a "heartbeat" rhythm for the system, or as a standard 64-bit counter. With automatic reload function and programmable clock source.

#### 2.5.15 Universal Synchronous/Asynchronous Receiver Transmitter (USART)

The product provides 4 sets of Universal Synchronous/Asynchronous Transceivers. Full duplex asynchronous communication, synchronous unidirectional communication, and half duplex single line communication are supported, as well as LIN (Local Interconnect Network), ISO7816 compatible smart card protocol and IrDA SIR ENDEC transmission codec specification, and modem (CTS/RTS hardware flow control) operation. It also allows multi-processor communication. It uses a fractional baud rate generator system and supports DMA operation for continuous communication.

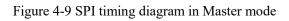

#### 2.5.16 Serial Peripheral Interface (SPI)

Up to 2 groups of serial peripherals interface (SPI) provide master or slave operation, dynamic switching. Support multi-master mode, full-duplex or half-duplex synchronous transmission, support basic SD card and MMC mode. Programmable clock polarity and phase, data bit width provides 8 or 16-bit selection, hardware CRC generation/check for reliable communication, and continuous communication support for DMA operation.

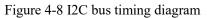

#### 2.5.17 I2C Bus

Up to 2 I2C bus interfaces can work in multi-master mode or Slave mode, perform all I<sup>2</sup>C Bus specific timing, protocol, arbitration, etc. It supports both standard and fast speed, and is compatible with SMBus2.0.

The I2C interface provides 7-bit or 10-bit addressing, and supports dual slave addressing in 7-bit Slave mode. It integrates built-in hardware CRC generator/checker. It also supports DMA operation and supports SMBus bus version 2.0 / PMBus bus.

#### 2.5.18 Controller Area Network (CAN)

The CAN interface is compatible with specifications 2.0A and 2.0B (active), the baud rate is up to 1Mbits/s, and it supports time-triggered communication functions. It can receive and send standard frames with 11-bit identifiers, as well as extended frames with 29-bit identifiers. It has 3 sending mailboxes and 2 3-level deep receiving FIFOs.

With 1 set of CAN controller products, there are only 14 configurable filters, and share a dedicated 512-byte SRAM memory with the USBD module for data transmission and reception. When USBD and CAN are used at the same time, in order to prevent access to SRAM conflicts, USBD can only use the lower 384 bytes.

#### 2.5.19 Universal Serial Bus Device (USBD)

The product is embedded with a USB2.0 full-speed controller, which complies with the USB2.0 full-speed standard. USBD provides 16 configurable USB device endpoints, supports low-speed devices and full-speed devices, supports control/batch/synchronization/interrupt transmission, double buffer mechanism, USB suspend/resume operations, and has standby/wake-up functions. The USB dedicated 48MHz clock is directly generated by the internal main PLL frequency division.

#### 2.5.20 Universal Serial Bus USB2.0 Full-speed Host/Device Controller (USBFS)

The USB2.0 full-speed host controller and device controller (USBFS) follow the USB2.0 full-speed standard. It provides 16 configurable USB device endpoints and a set of host endpoints. Support control/batch/synchronization/interrupt transmission, double buffer mechanism, USB bus suspend/resume operation, and provide standby/wake-up functions. The 48MHz clock dedicated to the USBFS module is directly generated by the internal main PLL frequency division (the PLL must be 144MHz or 96MHz or 48MHz).

#### 2.5.21 General-purpose Input and Output (GPIO)

The system provides 4 groups of GPIO ports with a total of 37 GPIO pins. Each pin can be configured by software as output (push-pull or open-drain), input (with or without pull-up or pull-down) or multiplexed peripheral function port. Most GPIO pins are shared with digital or analog multiplexed peripherals. Except for ports with analog input functions, all GPIO pins have high current passing capabilities. A locking mechanism is provided to freeze the IO configuration to avoid accidental writing to the I/O register.

Most of the I/O pins in the system are provided by  $V_{I'O}$ . Changing the  $V_{I'O}$  power supply will change the high value of the I/O pin output level to adapt to the external communication interface level. Please refer to the pin description for specific pins.

#### 2.5.22 Operational Amplifier/Comparator (OPA)

The product has built-in 2 groups of operational amplifiers/comparators, and the internal selection is linked to the ADC and TIMx peripherals. Its input and output can be selected by changing the configuration to select multiple channels. It supports to amplify the external analog small signal and send it to the ADC to realize the small signal ADC conversion. It can also complete the signal comparator function. The comparison result is output by GPIO or directly connected to the input channel of TIMx.

#### 2.5.23 2-wire SDI Serial Debug Interface

The core comes with a serial 2-wire serial debug interface (SDI), including SWDIO and SWCLK pins. The default debug interface pin function is turned on after system power on or reset, and SDI can be turned off as needed after the main program is running.

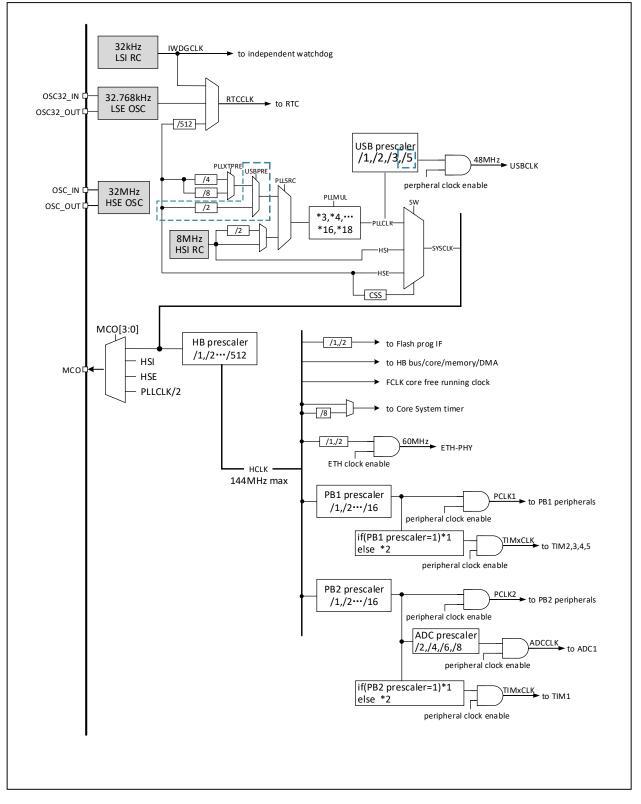

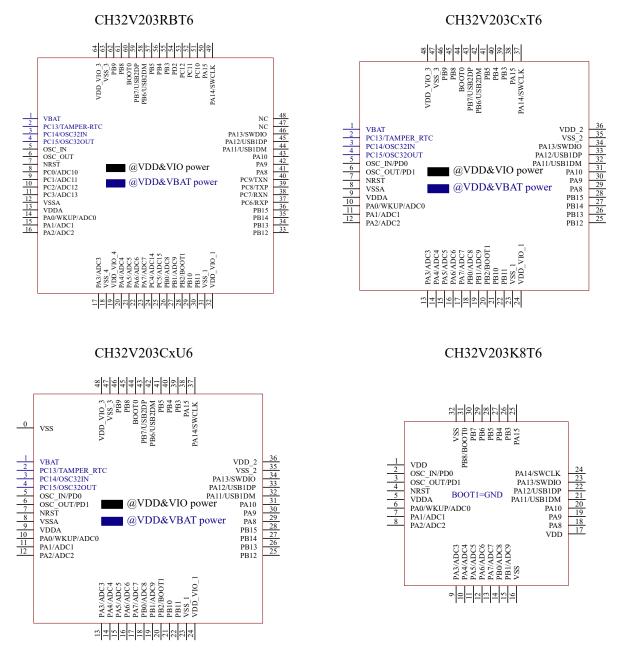

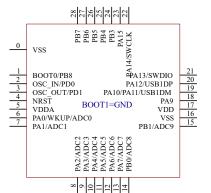

# **Chapter 3 Pinouts and Pin Definition**

## 3.1 Pinout

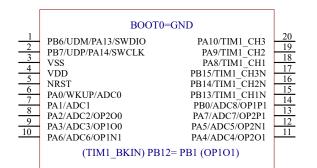

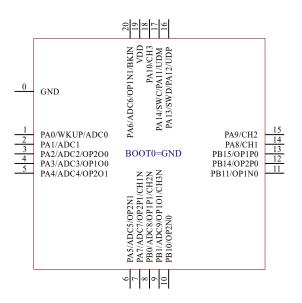

#### CH32V203G8R6

| $ \begin{array}{r} 1\\ 2\\ 3\\ 4\\ 5\\ 6\\ 7\\ 8\\ 9\\ 10\\ 11\\ 12\\ 13\\ 14\\ \end{array} $ | PA14/SWC/PB5/TIM3_CH2<br>PB6/U2DM/SCL/TIM4_CH1<br>PB7/U2DP/SDA/TIM4_CH2<br>BOOT0<br>PB8/TIM4_CH3<br>VDD<br>VSS<br>NRST<br>PA0/WKUP/ADC0<br>PA1/ADC1<br>PA2/ADC2/OP200<br>PA3/ADC3/OP100<br>PA6/ADC6/OP1N1<br>PB0/ADC8/OP1P1 | PA13/SWD/PA12/U1DP/CAN_TX/TIM1_ETR<br>PA11/U1DM/CAN_RX/TIM1_CH4<br>PA10/TIM1_CH3<br>PA9/TIM1_CH2<br>PA8/TIM1_CH2<br>PA8/TIM1_CH1<br>PB15/OP1P0/TIM1_CH3N<br>PB14/OP2P0/TIM1_CH3N<br>PB1/ADC9/OP1O1/PB12/TIM1_BKIN<br>PB1/ADC9/OP1O1/PB12/TIM1_BKIN<br>PB10/OP2N0<br>PA7/ADC7/OP2P1<br>PA5/ADC5/OP2N1<br>PA4/ADC4/OP2O1 | $\begin{array}{r} 28\\ \hline 27\\ \hline 26\\ \hline 25\\ \hline 24\\ \hline 23\\ \hline 22\\ \hline 21\\ \hline 20\\ \hline 19\\ \hline 18\\ \hline 17\\ \hline 16\\ \hline 15\\ \hline \end{array}$ |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

CH32V203G6U6

#### CH32V203F8P6

#### CH32V203F6P6

|                   | BOOT1<br>BOOT0/PB8<br>OSC_IN/PD0<br>OSC_OUT/PD1<br>NRST<br>VDDA<br>PA0/WKUP/ADC0 | PA14/SWCLK<br>PA13/SWDIO<br>PA12/USB1DP<br>PA11/USB1DM<br>VDD<br>VSS | 20<br>19<br>18<br>17<br>16<br>15         |

|-------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------|

| 7<br>8<br>9<br>10 | PA0/WKUP/ADC0<br>PA1/ADC1<br>PA2/ADC2<br>PA3/ADC3<br>PA4/ADC4                    | VSS<br>PB1/ADC9<br>PA7/ADC7<br>PA6/ADC6<br>PA5/ADC5                  | $\frac{13}{14}$<br>$\frac{13}{12}$<br>11 |

CH32V203F8U6

## **3.2 Pin Definitions**

#### Table 3-1 Pin definitions

Note: The pin function in the table below refer to all functions and do not involve specific model(s). There are differences in peripheral resources between different models. Please confirm whether this function is available according to the particular model's resource table before viewing this table.

|       | Pin No. |                   |                                        |                         |                  |                                |                                                                                     |                                                        |

|-------|---------|-------------------|----------------------------------------|-------------------------|------------------|--------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------|

| QFN20 | LQFP32  | LQFP48<br>QFN48X7 | Pin name                               | Pin type <sup>(1)</sup> | I/O<br>structure | Main function<br>(after reset) | Default alternate<br>function                                                       | Remapping<br>function <sup>(8)</sup>                   |

| -     | -       | 0                 | $V_{SS}$                               | Р                       | -                | V <sub>SS</sub>                |                                                                                     |                                                        |

| -     | -       | 1                 | V <sub>BAT</sub>                       | Р                       | -                | VBAT                           |                                                                                     |                                                        |

| -     | -       | 2                 | PC13-<br>TAMPER-<br>RTC <sup>(2)</sup> | I/O                     | -                | PC13 <sup>(3)</sup>            | TAMPER-RTC                                                                          |                                                        |

| -     | -       | 3                 | PC14-<br>OSC32_IN <sup>(2)</sup>       | I/O/A                   | -                | PC14 <sup>(3)</sup>            | OSC32_IN                                                                            |                                                        |

| -     | -       | 4                 | PC15-<br>OSC32_OUT <sup>(2)</sup>      | I/O/A                   | -                | PC15 <sup>(3)</sup>            | OSC32_OUT                                                                           |                                                        |

| -     | 2       | 5                 | OSC_IN                                 | I/A                     | -                | OSC_IN                         |                                                                                     | PD0 <sup>(4)</sup>                                     |

| -     | 3       | 6                 | OSC_OUT                                | O/A                     | -                | OSC_OUT                        |                                                                                     | PD1 <sup>(4)</sup>                                     |

| -     | 4       | 7                 | NRST                                   | Ι                       | -                | NRST                           |                                                                                     |                                                        |

| -     | -       | 8                 | V <sub>SSA</sub>                       | Р                       | -                | V <sub>SSA</sub>               |                                                                                     |                                                        |

| -     | 5       | 9                 | V <sub>DDA</sub>                       | Р                       | -                | V <sub>DDA</sub>               |                                                                                     |                                                        |

| 1     | 6       | 10                | PA0-WKUP                               | I/O/A                   | -                | PA0                            | WKUP<br>USART2_CTS<br>ADC_IN0<br>TIM2_CH1 <sup>(9)</sup><br>TIM2_ETR <sup>(9)</sup> | TIM2_CH1_2 <sup>(9)</sup><br>TIM2_ETR_2 <sup>(9)</sup> |

| 2     | 7       | 11                | PA1                                    | I/O/A                   | -                | PA1                            | USART2_RTS<br>ADC_IN1<br>TIM2_CH2                                                   | TIM2_CH2_2                                             |

| 3     | 8       | 12                | PA2                                    | I/O/A                   | -                | PA2                            | USART2_TX<br>ADC_IN2<br>TIM2_CH3<br>OPA2_OUT0                                       | TIM2_CH3_1                                             |

| 4     | 9       | 13                | PA3                                    | I/O/A                   | -                | PA3                            | USART2_RX<br>ADC_IN3<br>TIM2_CH4<br>OPA1_OUT0                                       | TIM2_CH4_1                                             |

| 5     | 10      | 14                | PA4                                    | I/O/A                   | -                | PA4                            | SPI1_NSS<br>USART2_CK                                                               |                                                        |

#### Table 3-1-1 QFN20/LQFP32/LQFP48/QFN48X7 pin definitions

|          | Pin No. |                   |                      |                 |                  |                                |                               |                                      |

|----------|---------|-------------------|----------------------|-----------------|------------------|--------------------------------|-------------------------------|--------------------------------------|

| QFN20    | LQFP32  | LQFP48<br>QFN48X7 | Pin name             | Pin type<br>(1) | I/O<br>structure | Main function<br>(after reset) | Default alternate<br>function | Remapping<br>function <sup>(8)</sup> |

|          |         |                   |                      |                 |                  |                                | ADC_IN4                       |                                      |

|          |         |                   |                      |                 |                  |                                | OPA2_OUT1                     |                                      |

|          |         |                   |                      |                 |                  |                                | SPI1_SCK                      |                                      |

| 6        | 11      | 15                | PA5                  | I/O/A           | -                | PA5                            | ADC_IN5                       | USART4_TX_1                          |

|          |         |                   |                      |                 |                  |                                | OPA2_CH1N                     |                                      |

|          |         |                   |                      |                 |                  |                                | SPI1_MISO                     |                                      |

| 20       | 12      | 16                | PA6                  | I/O/A           |                  | PA6                            | ADC_IN6                       | TIM1_BKIN_1                          |

| 20       | 12      | 10                | 140                  | I/O/A           | _                | 140                            | TIM3_CH1                      | USART4_CK_1                          |

|          |         |                   |                      |                 |                  |                                | OPA1_CH1N                     |                                      |

|          |         |                   |                      |                 |                  |                                | SPI1_MOSI                     | TIM1_CH1N_1                          |

| 7        | 13      | 17                | PA7                  | I/O/A           | _                | PA7                            | ADC_IN7                       | USART4 CTS                           |

| <i>'</i> | 15      | 17                | 1717                 | 1.0/11          | _                | 1717                           | TIM3_CH2                      | 1                                    |

|          |         |                   |                      |                 |                  |                                | OPA2_CH1P                     | 1                                    |

|          |         |                   |                      |                 |                  |                                | ADC_IN8                       |                                      |

| 8        | 14      | 18                | PB0                  | I/O/A           | _                | PB0                            | TIM3_CH3                      | TIM1_CH2N_1                          |

| 0        | 17      | 10                | 100                  | 1.0/11          | _                | 1 00                           | OPA1_CH1P                     | TIM3_CH3_2                           |

|          |         |                   |                      |                 |                  |                                | USART4_TX                     |                                      |

|          |         |                   |                      |                 |                  |                                | ADC_IN9                       |                                      |

| 9        | 15      | 19                | PB1                  | I/O/A           | _                | PB1                            | TIM3_CH4                      | TIM1_CH3N_1                          |

| Í        | 10      | 17                | 121                  | 1.0/11          |                  | 1.51                           | OPA1_OUT1                     | TIM3_CH4_2                           |

|          |         |                   |                      |                 |                  |                                | USART4_RX                     |                                      |

| -        | -       | 20                | PB2 <sup>(5)</sup>   | I/O             | FT               | PB2                            | USART4 CK                     |                                      |

|          |         |                   |                      |                 |                  | BOOT1 <sup>(5)</sup>           |                               |                                      |

|          |         |                   |                      |                 |                  |                                | I2C2_SCL                      | TIM2_CH3_2                           |

| 10       | -       | 21                | PB10                 | I/O/A           | FT               | PB10                           | USART3_TX                     | TIM2_CH3_3                           |

|          |         |                   |                      |                 |                  |                                | OPA2_CH0N                     |                                      |

|          |         |                   | 22.4                 | <b>T</b> (0,1)  |                  | 22.4                           | I2C2_SDA                      | TIM2_CH4_2                           |

| 11       | -       | 22                | PB11                 | I/O/A           | FT               | PB11                           | USART3_RX                     | TIM2_CH4_3                           |

|          |         |                   |                      |                 |                  |                                | OPA1_CH0N                     |                                      |

| -        | -       | 23                | V <sub>SS_1</sub>    | Р               | -                | V <sub>SS_1</sub>              |                               |                                      |

| -        | 16      |                   | V <sub>SS</sub>      | P               | -                | V <sub>SS</sub>                |                               |                                      |

| -        | -       | 24                | V <sub>DD_IO_1</sub> | P               | -                | V <sub>DD_IO_1</sub>           |                               |                                      |

| -        | 17      |                   | V <sub>DD</sub> _    | Р               | -                | V <sub>DD</sub> _              |                               |                                      |

|          |         |                   |                      |                 |                  |                                | SPI2_NSS                      |                                      |

| -        | -       | 25                | PB12                 | I/O/A           | FT               | PB12                           | I2C2_SMBA                     |                                      |

|          |         |                   |                      |                 |                  |                                | USART3_CK                     |                                      |

|          |         |                   |                      |                 |                  |                                | TIM1_BKIN                     |                                      |

|          |         |                   | DD 1 2               |                 | FT               | DD 12                          | SPI2_SCK                      |                                      |

| -        | -       | 26                | PB13                 | I/O/A           | FT               | PB13                           | USART3_CTS                    |                                      |

|          |         |                   |                      |                 |                  |                                | TIM1_CH1N                     | <u> </u>                             |

|       | Pin N  | lo.               |            |                         |                  |                                |                                                   |                                                                                                                                                    |

|-------|--------|-------------------|------------|-------------------------|------------------|--------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| QFN20 | LQFP32 | LQFP48<br>QFN48X7 | Pin name   | Pin type <sup>(1)</sup> | I/O<br>structure | Main function<br>(after reset) | Default alternate<br>function                     | Remapping<br>function <sup>(8)</sup>                                                                                                               |

| 12    | -      | 27                | PB14       | I/O/A                   | FT               | PB14                           | SPI2_MISO<br>TIM1_CH2N<br>USART3_RTS<br>OPA2_CH0P |                                                                                                                                                    |

| 13    | -      | 28                | PB15       | I/O/A                   | FT               | PB15                           | SPI2_MOSI<br>TIM1_CH3N<br>OPA1_CH0P               |                                                                                                                                                    |

| 14    | 18     | 29                | PA8        | I/O                     | FT               | PA8                            | USART1_CK<br>TIM1_CH1<br>MCO                      | USART1_CK_1<br>TIM1_CH1_1                                                                                                                          |

| 15    | 19     | 30                | PA9        | I/O                     | FT               | PA9                            | USART1_TX<br>TIM1_CH2                             | TIM1_CH2_1                                                                                                                                         |

| 18    | 20     | 31                | PA10       | I/O                     | FT               | PA10                           | USART1_RX<br>TIM1_CH3                             | TIM1_CH3_1                                                                                                                                         |

| 17    | 21     | 32                | PA11       | I/O/A                   | FT               | PA11                           | USART1_CTS<br>USBDM<br>CAN1_RX<br>TIM1_CH4        | USART1_CTS_<br>1<br>TIM1_CH4_1                                                                                                                     |

| 16    | 22     | 33                | PA12       | I/O/A                   | FT               | PA12                           | USART1_RTS<br>USBDP<br>CAN1_TX<br>TIM1_ETR        | USART1_RTS_<br>1<br>TIM1_ETR_1                                                                                                                     |

|       | 23     | 34                | PA13       | I/O                     | FT               | SWDIO                          |                                                   | PA13                                                                                                                                               |

| -     | -      | 35                | $V_{SS_2}$ | Р                       | -                | V <sub>SS_2</sub>              |                                                   |                                                                                                                                                    |

| -     | -      | 36                | $V_{DD_2}$ | Р                       | -                | V <sub>DD_2</sub>              |                                                   |                                                                                                                                                    |

| 17    | 24     | 37                | PA14       | I/O                     | FT               | SWCLK                          |                                                   | PA14                                                                                                                                               |

| -     | 25     | 38                | PA15       | I/O                     | FT               | PA15                           |                                                   | TIM2_CH1_1 <sup>(9)</sup><br>TIM2_ETR_1 <sup>(9)</sup><br>TIM2_CH1_3 <sup>(9)</sup><br>TIM2_ETR_3 <sup>(9)</sup><br>SPI1_NSS_1<br>USART4_RTS_<br>1 |

| -     | 26     | 39                | PB3        | I/O                     | FT               | PB3                            | USART4_CTS                                        | TIM2_CH2_1<br>TIM2_CH2_3<br>SPI1_SCK_1                                                                                                             |

| -     | 27     | 40                | PB4        | I/O                     | FT               | PB4                            | USART4_RTS                                        | TIM3_CH1_2<br>SPI1_MISO                                                                                                                            |

|       | Pin No. |                   |                   |                 |                  |                                |                                  |                                          |

|-------|---------|-------------------|-------------------|-----------------|------------------|--------------------------------|----------------------------------|------------------------------------------|

| QFN20 | LQFP32  | LQFP48<br>QFN48X7 | Pin name          | Pin type<br>(1) | I/O<br>structure | Main function<br>(after reset) | Default alternate<br>function    | Remapping<br>function <sup>(8)</sup>     |

| -     | 28      | 41                | PB5               | I/O             | FT               | PB5                            | I2C1_SMBA                        | TIM3_CH2_2<br>SPI1_MOSI_1<br>USART4_RX_1 |