# CH32L103 Reference Manual

V1.9 https://wch-ic.com

### Overview

CH32L103 is an industrial-grade general-purpose microcontroller based on 32-bit RISC-V instruction set and architecture. Adopting QingKe V4C core, it supports hardware interrupt stack and improves interrupt response efficiency. This series of products are loaded with rich peripheral interfaces and functional modules. Its internal organizational structure meets the low-cost and low-power embedded application scenarios.

This manual is aimed at user's application development and provides detailed information about the use of CH32L103 products.

| Features<br>Core<br>versions | Instruction<br>set | Hardware<br>stack<br>levels | Interrupt<br>nesting<br>levels | Fast<br>interrupt<br>channels | Integer<br>division<br>cycles | Vector table model | Extended instruction | Memory<br>protection |

|------------------------------|--------------------|-----------------------------|--------------------------------|-------------------------------|-------------------------------|--------------------|----------------------|----------------------|

| QingKeV4B                    | IMAC               | 2                           | 2                              | 4                             | 9                             | Address or command | Supported            | None                 |

| QingKeV4C                    | IMAC               | 2                           | 2                              | 4                             | 5                             | Address or command | Supported            | Standard             |

| QingKeV4F                    | IMAFC              | 3                           | 8                              | 4                             | 5                             | Address or command | Supported            | Standard             |

#### **RISC-V** core version comparison overview

| Register bit<br>attributes | Property description                                          |

|----------------------------|---------------------------------------------------------------|

| RF                         | Read-only attribute, read a fixed value.                      |

| RO                         | Read-only attribute, changed by hardware.                     |

| RZ                         | Read-only attribute, auto bit clear 0 after read operation.   |

| WO                         | Write only attribute (not readable, read value uncertain)     |

| WA                         | Write-only attribute, writable in Safe mode.                  |

| WZ                         | Write only attribute, auto bit clear 0 after write operation. |

| RW                         | Readable and writable.                                        |

| RWA                        | Readable, writable in Safe mode.                              |

| RW1                        | Readable, write 1 valid, write 0 invalid.                     |

| RW0                        | Readable, write 0 valid, write 1 invalid.                     |

| RW1T                       | Readable, write 0 invalid, write 1 flipped.                   |

| SC                         | Auto cleared.                                                 |

### Abbreviated description of the bit attribute in the register:

### **Chapter 1 Memory and Bus Architecture**

#### **1.1 Bus Architecture**

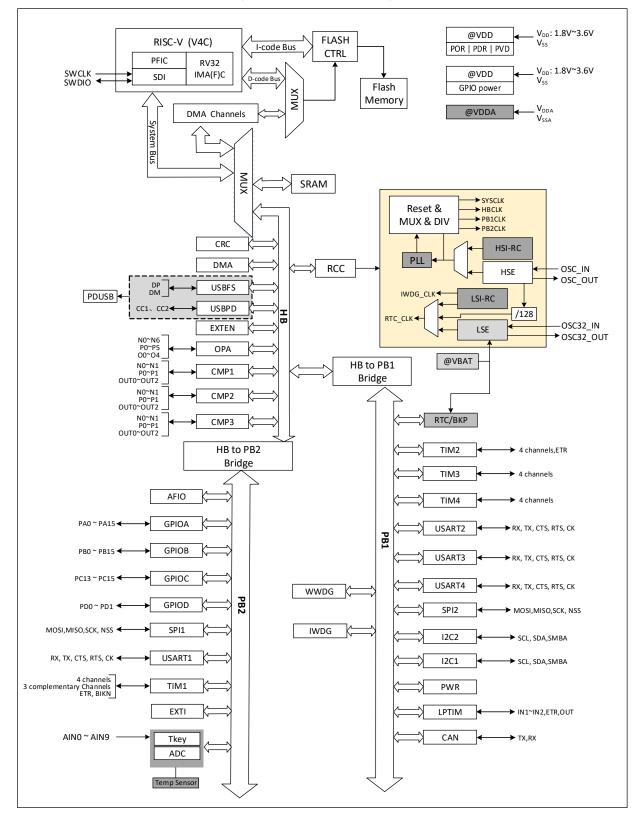

This series of products are general-purpose microcontrollers designed based on the RISC-V instruction set, and the core, arbitration unit, DMA module, SRAM storage and other parts of its architecture interact with each other through multiple sets of buses. Its system block diagram is shown in Figure 1-1.

#### Figure 1-1 System block diagram

The system is equipped with: General-purpose DMA controller to reduce the CPU burden and improve efficiency; clock tree hierarchy management to reduce the total power consumption of peripherals, as well as data protection mechanisms, clock security system protection mechanisms and other measures to increase system stability.

### 1.2 Memory Map

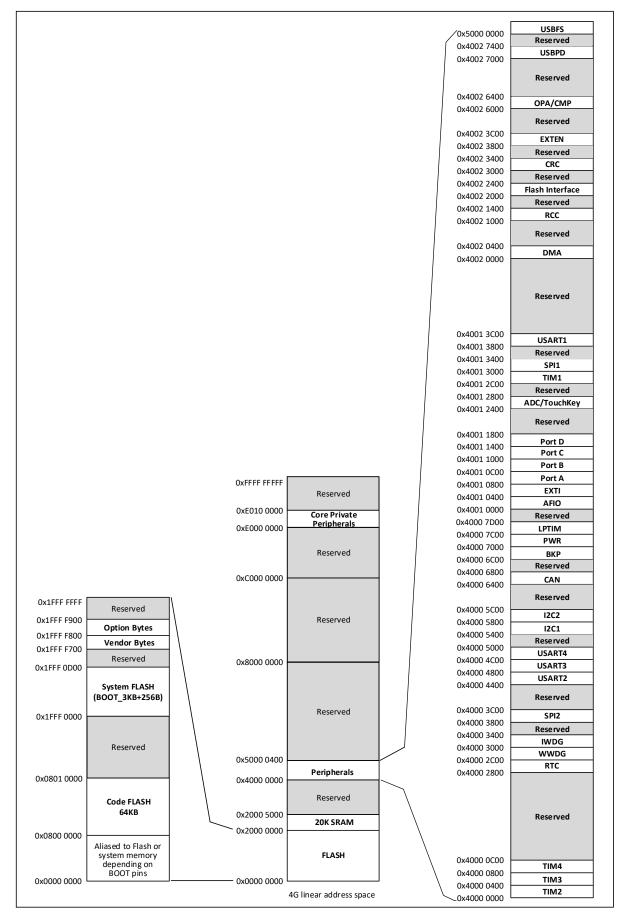

The CH32L103 family contains program memory, data memory, core registers, peripheral registers, and more, all addressed in a 4GB linear space.

System storage stores data in small-end format, i.e., low bytes are stored at the low address and high bytes are stored at the high address.

Figure 1-2 Storage image

#### **1.2.1 Memory Allocation**

Built-in 20KB SRAM, starting address 0x20000000, supports byte, half-word (2 bytes), and full-word (4 bytes) access.

Built-in up to 64KB program Flash memory (CodeFlash) for storing user applications.

Built-in 3K+256B System memory (Bootloader) for storing the system bootloader (Factory-cured bootloader).

Built-in 256B space for vendor configuration word storage, factory-cured and unmodifiable by users.

Built-in 256B space for user option bytes storage.

#### **1.3 Boot Configuration**

The system can select 3 different boot modes via the BOOT0 and BOOT1 pins.

| BOOT0 | BOOT1 | Boot Mode                      |  |  |  |  |  |  |  |  |  |  |  |

|-------|-------|--------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 0     | X     | Boot from Program Flash Memory |  |  |  |  |  |  |  |  |  |  |  |

| 1     | 0     | Boot from System Memory        |  |  |  |  |  |  |  |  |  |  |  |

| 1     | 1     | Boot from internal SRAM        |  |  |  |  |  |  |  |  |  |  |  |

Table 1-1 Boot Mode

The user selects the boot mode after a reset by setting the status value of the BOOT pin. A system reset or a power reset causes the value of the BOOT pin to be relocked.

The program flash memory, system memory and internal SRAM are accessed differently depending on the boot mode:

- When booted from Program Flash Memory, the program flash memory address is mapped to the 0x00000000 address area and is also able to be accessed in the original address area 0x08000000.

- When booted from System Memory, the system memory address is mapped to the 0x00000000 address area and is also accessible in the original address area 0x1FFF0000.

- Booting from internal SRAM is only accessible from the 0x20000000 address area.

V1.9

### **Chapter 2 Power Control (PWR)**

### 2.1 Overview

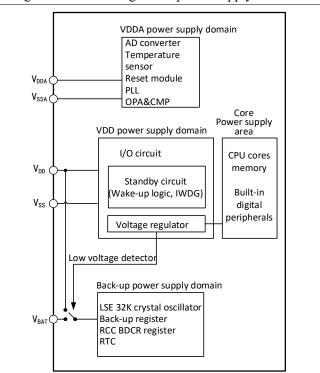

The system operating voltage  $V_{DD}$  ranges from 1.8 to 3.6 V. The built-in voltage regulator provides the low-voltage power supply required by the core. When the main power supply,  $V_{DD}$ , is powered down, a backup power source such as a battery can provide power for the real-time clock (RTC) and backup registers through the  $V_{BAT}$  pin. If no backup power is required, it is recommended that  $V_{DD}$  be connected directly to the  $V_{BAT}$  pin.

The  $V_{DDA}$  and  $V_{SSA}$  pins are dedicated to powering analog-related circuits in the system, including ADC, temperature sensor, etc.

Figure 2-1 Block diagram of power supply structure

After the main power supply  $V_{DD}$  is powered down, the analog switch is switched to  $V_{BAT}$  and the backup domain is powered by the  $V_{BAT}$  pin, at this time, PC13 to 15 cannot be used as GPIOs, and only the following functions can be used:

- PC13 can be used as TAMPER pin, RTC alarm clock or second output.

- PC14 and PC15 can only be used as LSE pins.

When the main power supply VDD is powered on stably, the system automatically switches the backup area to be powered by VDD, and PC13~15 can be used as a GPIO function.

When the PC13~15 pin is output as a GPIO, the speed must be limited to less than 2MHz, the maximum load capacitance must be 30pF, and must not be used in continuous output and suction current situations, such as LED drive.

Note: In the process of restoring the power supply of the main power supply  $V_{DD}$ , the internal  $V_{BAT}$  power supply is still connected to the external standby power supply through the corresponding  $V_{BAT}$  pins. If the  $V_{DD}$  is stable within

less than the reset lag time  $t_{RSTTEMPO}$  and is more than 0.6V higher than the value of  $V_{BAT}$ , then there may be a short moment when the current is pumped into the  $V_{BAT}$  through the diode between the  $V_{DD}$  and the  $V_{BAT}$ , and then injected into the battery and other backup power through the  $V_{BAT}$  pin. If the backup power supply cannot withstand such instantaneous injection current, it is recommended to add a forward turn-on low voltage drop diode between the backup power supply and the  $V_{BAT}$  pin.

### 2.2 Power Management

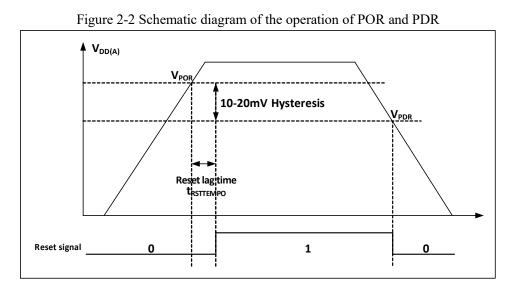

#### 2.2.1 Power-on Reset and Power-down Reset

The system integrated a power-on reset POR and a power-down reset PDR circuit. When the chip supply voltage  $V_{DD}$  falls below the corresponding threshold voltage, the system is reset by the relevant circuit, and no additional external reset circuit is required. Please refer to the corresponding datasheet for the parameters of the power-on threshold voltage  $V_{POR}$  and the power-down threshold voltage  $V_{PDR}$ .

#### 2.2.2 Programmable Voltage Detector

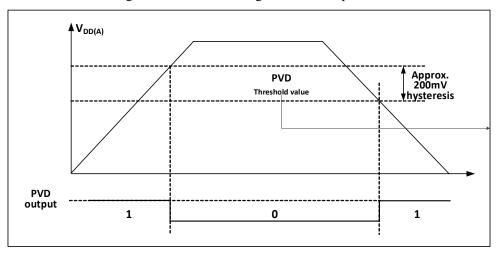

The programmable voltage detector, PVD, is mainly used to monitor the change of the main power supply of the system, compared with the threshold voltage set by PLS[2:0] of the power control register PWR\_CTLR, and together with the setting of the external interrupt register (EXTI), the relevant interrupt can be generated in order to notify the system to carry out the pre-dropout operation, such as the data saving, in time.

The specific configuration is as follows:

1) Set the PLS[2:0] fields of the PWR\_CTLR register to select the voltage threshold to be monitored.

2) Optional interrupt handling. the PVD function internally connects to the rising/falling edge trigger setting on line 16 of the EXTI module, turns on this interrupt (configures EXTI), and generates a PVD interrupt when  $V_{DD}$  falls below the PVD threshold or rises above the PVD threshold.

3) Set the PVDE bit of the PWR\_CTLR register to enable the PVD function.

4) Read the PVD0 bit of PWR\_CSR status register to obtain the relationship between the current system main power supply and the threshold value set by PLS[2:0], and perform the corresponding soft processing. When the  $V_{DD}$  voltage is higher than the PLS[2:0] setting threshold, the PVD0 position is 0; when the V<sub>DD</sub> voltage is lower than the PLS[2:0] setting threshold, the PVD0 position is 1.

Figure 2-3 Schematic diagram of PVD operation

### 2.3 Low-power Modes

After a system reset, the microcontroller is in a normal operating state (run mode), where system power can be saved by reducing the system main frequency or turning off the unused peripheral clock or reducing the operating peripheral clock. If the system does not need to work, you can set the system to enter low-power mode and let the system jump out of this state by specific events.

Microcontrollers currently offer 3 low-power modes, divided in terms of operating differences between processors, peripherals, voltage regulators, etc.

- Sleep mode: The core stops running and all peripherals (including core private peripherals) are still running.

- Stop mode: Stops all clocks and the system continues to run after waking up. Stop mode is divided into 4 gears, respectively: Stop mode 1, Stop mode 2, Stop mode 3, Stop mode 4, the corresponding configuration method is shown in Table 2-1, stop mode four gears after the configuration of the current reference CH32L103DS0 manual.

- Standby mode: Stop all clocks and reset the microcontroller after wakeup (power reset).

| Mode  | Entry                                                  | Wake-up source                                                                                                                                                                 | Effect on clock                                  | Voltage regulator                                                                                                                     |

|-------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| CLEED | WFI                                                    | Any interrupt                                                                                                                                                                  | Core clock OFF,                                  | NJ 1                                                                                                                                  |

| SLEEP | WFE                                                    | Wake-up event                                                                                                                                                                  | no effect on other clocks                        | Normal                                                                                                                                |

|       |                                                        |                                                                                                                                                                                |                                                  | Stop mode1:<br>LPDS=0, PDDS=0                                                                                                         |

| STOP  | Set SLEEPDEEP<br>to 1<br>Clear PDDS to 0<br>WFI or WFE | Any external interrupt/event,<br>NRST pin reset, PVD output,<br>RTC alarm event, USB wake-<br>up signal, USB PD wake-up<br>signal, CMP wake-up signal,<br>LPTIM wake-up signal | Disable HSE,<br>HIS, PLL and<br>peripheral clock | Stop mode 2 (LDO<br>energy saving<br>mode): LPDS=0,<br>PDDS=0,<br>AUTO_LDO_EC=1<br>or LPDS=0,<br>LDO_EC=1<br>Stop mode 3:<br>RAMLV=0, |

|         |                                                      |                                                                                                                                                                                                                           |                                                  | PDDS=0, LPDS=1                             |

|---------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------|

|         |                                                      |                                                                                                                                                                                                                           |                                                  | Stop mode 4:<br>RAMLV=1,<br>PDDS=0, LPDS=1 |

| STANDBY | Set SLEEPDEEP<br>to 1<br>Set PDDS to 1<br>WFI or WFE | WKUP pin rising edge, RTC<br>alarm event, NRST pin reset,<br>IWDG reset, PVD's output.<br>Note: Any of the<br>EXTI0~EXTI17 external events<br>can also wake up the system,<br>but the system is reset after<br>waking up. | Disable HSE,<br>HIS, PLL and<br>peripheral clock | Off                                        |

Note: The SLEEPDEEP bit belongs to the core private peripheral control bit, reference PFIC\_SCTLR register.

#### 2.3.1 Low-power Configuration Options

#### • WFI and WFE

WFI: The microcontroller is woken up by an interrupt source with interrupt controller response, and the interrupt service function will be executed first after the system wakes up (except for microcontroller reset).

WFE: The wakeup event triggers the microcontroller to exit low-power mode. Wake-up events include:

- 1) Configure an external or internal EXTI line to event mode, when no interrupt controller needs to be configured.

- 2) Or configure an interrupt source, equivalent to a WFI wakeup, where the system prioritizes the execution of the interrupt service function.

- 3) Or configure the SEVONPEND bit to turn on peripheral interrupt enable, but not interrupt enable in the interrupt controller, and the interrupt pending bit needs to be cleared after the system wakes up.

- SLEEPONEXIT

Enable: After executing the WFI or WFE instruction, the microcontroller ensures that all pending interrupt services are exited and then enters low-power mode.

Disable: The microcontroller enters low-power mode immediately after executing the WFI or WFE command.

• SEVONPEND

Enable: All interrupts or wake-up events can wake up the low-power consumption entered by executing WFE. Disable: Only interrupts or wake-up events enabled in the interrupt controller can wake up the low-power consumption entered by executing WFE.

#### 2.3.2 Sleep Mode

In this mode, all IO pins keep their state in Run mode and all peripheral clocks are normal, so try to turn off useless peripheral clocks before entering Sleep mode to reduce low-power consumption. This mode takes the shortest time to wake up.

Enter: Configure core register control bit SLEEPDEEP=0, power control register PDDS=0, execute WFI or WFE, optionally SEVONPEND and SLEEPONEXIT.

Exit: Arbitrary interrupt or wakeup event.

#### 2.3.3 Stop Mode

Stop mode is a combination of peripheral clock control mechanisms based on the core's deep sleep mode

(SLEEPDEEP) and allows the voltage regulator to operate in a much lower power consumption state. In this mode the high frequency clock (HSE/HSI/PLL) domain is switched off, the SRAM and register contents are maintained and the IO pin state is held. The system can continue to run after this mode wakes up and the HSI is called the default system clock.

If flash programming is in progress, the system does not enter stop mode until access to memory is complete; if access to the PB is in progress, the system does not enter stop mode until access to the APB is complete.

Workable modules in stop mode: Independent Watchdog Dog (IWDG), Real Time Clock (RTC), Low Frequency Clock (LSI/LSE), Low Power Timer (LPTIM).

Entry: Configuration of the core register control bit SLEEPDEEP=1, PDDS=0 of the power control register, optional LPDS bit, execution of WFI or WFE, optional SEVONPEND and SLEEPONEXIT. Before entering the STOP voltage regulator low-power mode (PDDS=0, LPDS=1), preset FLASH\_LP[1:0] = 10b, i.e. FLASH low power mode 1.

Exit: Any external interrupt/event, external reset on the NRST pin, output of PVD, RTC alarm clock, wake-up signal for USB, wake-up signal for USB PD, wake-up signal for CMP, wake-up signal for LPTIM, and so on.

Different levels of stop mode are selected through different configurations. In stop mode, i.e., PDDS=0 and optional LPDS bit, LPDS=0, the voltage regulator works in stop mode 1; LPDS=0, AUTO\_LDO\_EC=1, the power system will automatically save energy when the MCU enters stop mode, i.e., it enters stop mode 2, or LPDS=0, LDO\_EC=1, also stop mode 2; LPDS=1, the voltage regulator operates in Stop Mode 3. Based on Stop Mode 3, the power consumption is minimized by enabling RAM low voltage mode by configuring RAMLV=1 in PWR\_CTLR register, which is called Stop Mode 4.

#### 2.3.4 Standby Mode

The only difference between the Standby mode and the stop mode is that the microcontroller will be reset after exiting under certain specified wake-up conditions and a power reset is performed.

Modules that can work in Standby mode: Independent Watchdog (IWDG), Real Time Clock (RTC), Low Frequency Clock (LSI/LSE).

Entry: Configure the core register control bits SLEEPDEEP = 1, PDDS = 1 for the power control register, perform WFI or WFE, optional SEVONPEND and SLEEPONEXIT, and preset FLASH\_LP[1:0] = 10b before entering STANDBY mode, i.e., FLASH low-power mode 1.

Exit:

1) EXTI0~EXTI18 Any external event (exclude interrupt), the microcontroller performs a power reset after this wakeup.

2) Rising edge of WKUP pin, rising edge of RTC alarm event, external reset on NRST pin, IWDG reset, output of PVD, RTC alarm, the microcontroller performs power reset after this wake-up.

In Standby mode, when normal power supply is used, 2K bytes of RAM are not powered down by configuring R2KSTY=1 of PWR\_CTLR register, and 18K bytes of RAM are not powered down by configuring R18KSTY=1 of PWR\_CTLR register; when VBAT power supply is used, 2K bytes of RAM are not powered down by configuring R2KVBAT=1 of PWR\_CTLR register and R18KVBAT=1 to control 18K bytes of RAM from being powered down. On top of that, power consumption can be minimized by configuring RAMLV=1 of PWR\_CTLR register to enable RAM low voltage mode.

*Note: Putting the microprocessor into Stop or Standby mode in debug mode will lose the debug connection.* R2KSTY=1 controls the address range of 2K byte RAM: 0x20000000-0x20000000+2K R18KSTY=1 controls the address range of 18K bytes of RAM: 0x20000000+2K-0x20000000+2K+18K

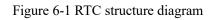

#### 2.3.5 RTC Auto-wakeup

RTC can automatically wake up without external interruption. By programming the time base, it can be awakened periodically from Stop or Standby mode.

The accurate external low frequency 32.768KHz crystal oscillator LSE can be selected as the RTC clock source, or the internal LSI oscillator can be selected as the RTC clock source. The accuracy and power consumption index of LSI is worse than that of LSE.

The RTC alarm clock event can wake the MCU from downtime mode. In order to achieve this function, the external break line 17 needs to be configured, and the RTC needs to be set to generate alarm clock events. To wake up from Standby mode, simply set RTC to generate an alarm clock event.

#### 2.3.6 FLASH Low-power Mode

Before entering the FLASH low-power mode, it is necessary to enable the FLASH to enter the low-power mode by setting the FLASH\_LP\_REG bit 1 of the power control register (PWR\_CTLR), and then set the FLASH\_LP bit of the power control register (PWR\_CTLR). At this point, the configuration of the MCU's FLASH low-power mode is complete.

#### **2.4 Register Description**

| Table 2-2 PWR-related registers list |                |                               |             |  |  |  |  |  |  |  |  |

|--------------------------------------|----------------|-------------------------------|-------------|--|--|--|--|--|--|--|--|

| Name                                 | Access address | Description                   | Reset value |  |  |  |  |  |  |  |  |

| R32_PWR_CTLR                         | 0x40007000     | Power control register        | 0x00000400  |  |  |  |  |  |  |  |  |

| R32_PWR_CSR                          | 0x40007004     | Power control/status register | 0x00000000  |  |  |  |  |  |  |  |  |

#### 2.4.1 Power Control Register (PWR\_CTLR)

| 31  | 30        | 29         | 28              | 27  | 26        | 25               | 24      | 23 22 21     | 20        | 19               | 18          | 17              | 16         |

|-----|-----------|------------|-----------------|-----|-----------|------------------|---------|--------------|-----------|------------------|-------------|-----------------|------------|

|     | Reserved  |            |                 |     |           |                  |         |              | RAM<br>LV | R18K<br>VBA<br>T | R2K<br>VBAT | R18<br>K<br>STY | R2K<br>STY |

| 15  | 14        | 13         | 12              | 11  | 10        | 9                | 8       | 7 6 5        | 4         | 3                | 2           | 1               | 0          |

| Res | erve<br>d | LDO_E<br>C | AUTO_LDO_E<br>C | FLA | SH_L<br>P | FLASH_LP_RE<br>G | DB<br>P | PLS[2:0<br>] | PVD<br>E  | CSB<br>F         | CWU<br>F    | PDD<br>S        | LPD<br>S   |

| Bit     | Name     | Access | Description                                                                                                    | Reset value |

|---------|----------|--------|----------------------------------------------------------------------------------------------------------------|-------------|

| [31:21] | Reserved | RO     | Reserved                                                                                                       | 0           |

| 20      | RAMLV    |        | RAM operates in low voltage mode enable control bit<br>(relatively lower power consumption):<br>1: On; 0: Off. | 0           |

| 19      | R18KVBAT | RW     | 18K RAM power switch control bit in Standby mode when                                                          | 0           |

|         |            |       | VBAT is powered:                                             |      |

|---------|------------|-------|--------------------------------------------------------------|------|

|         |            |       | 1: Powered; 0: Not powered.                                  |      |

|         |            |       | 2K RAM power switch control bit in Standby mode when         |      |

| 18      | R2KVBAT    | RW    | VBAT is powered:                                             | 0    |

|         |            |       | 1: Powered; 0: Not powered.                                  |      |

| 17      | DISKOTY    | DW    | Standby mode 18K RAM power switch control bit:               | 0    |

| 17      | R18KSTY    | RW    | 1: Powered; 0: Not powered.                                  | 0    |

| 16      | R2KSTY     | RW    | Standby mode 2K RAM power switch control bit:                | 0    |

| 16      | K2K51 I    | ĸw    | 1: Powered; 0: Not powered.                                  | 0    |

| [15:14] | Reserved   | RO    | Reserved                                                     | 0    |

|         |            |       | Power system LDO energy saving mode enable:                  |      |

|         |            |       | 1: Energy saving is turned on, approximately 10µA            |      |

| 12      |            | RW    | reduction;                                                   | 0    |

| 13      | LDO_EC     | ĸw    | 0: Does not turn on.                                         | 0    |

|         |            |       | Note: When this bit is turned on, it only supports a maximum |      |

|         |            |       | total current of no more than 2mA.                           |      |

|         |            |       | Preset LDO energy saving mode after entering stop mode:      |      |

| 12      | AUTO_LDO_  | RW    | 1: Automatic energy saving when entering stop mode, i.e.     | 0    |

| 12      | EC         | ĸw    | stop mode 2;                                                 | 0    |

|         |            |       | 0: Normal LDO mode.                                          |      |

|         |            |       | Configure the FLASH mode:                                    |      |

|         |            |       | 00: Idle mode;                                               |      |

|         |            |       | X1: FLASH low-power mode 0;                                  |      |

| F11 101 |            | DW    | 10: FLASH low power mode 1.                                  | 011  |

| [11:10] | FLASH_LP   | RW    | Note: This bit is preset to FLASH Low Power Mode 1           | 01b  |

|         |            |       | (FLASH_LP[1:0] = 10b) before entering STANDBY mode or        |      |

|         |            |       | STOP Voltage Regulator Low Power Mode (PDDS=0,               |      |

|         |            |       | LPDS=1).                                                     |      |

|         |            |       | In combination with the FLASH_LP field, the software         |      |

|         |            |       | configures the enable for FLASH to enter low-power mode:     |      |

| 9       | FLASH_LP_R | RW    | 1: FLASH can be enabled to enter low power mode;             | 0    |

|         | EG         |       | 0: It is not possible to enable FLASH to enter low-power     |      |

|         |            |       | mode by software.                                            |      |

|         |            |       | Write enable for the backup domain. This bit must be set to  |      |

|         |            |       | 1 when the RTC clock is the 128th division of the external   |      |

| 8       | DBP        | RW    | clock.                                                       | 0    |

|         |            |       | 1: Write of the RTC and backup registers is allowed;         |      |

|         |            |       | 0: Write of the RTC and backup registers is prohibited.      |      |

|         |            |       | PVD voltage monitoring threshold setting. See the Electrical |      |

|         |            |       | Characteristics section of the datasheet for a detailed      |      |

| [7.5]   | PLS[2:0]   | RW    | description.                                                 | 000b |

| [7:5]   |            | 17.44 | 000: Rising edge 1.75V/falling edge 1.70V;                   | 0000 |

|         |            |       | 001: Rising edge 1.93V/Falling edge 1.87V;                   |      |

|         |            |       | 010: Rising edge 2.14V/Falling edge 2.08V;                   |      |

|   |       | 1    |                                                             |   |

|---|-------|------|-------------------------------------------------------------|---|

|   |       |      | 011: Rising edge 2.35V/falling edge 2.28V;                  |   |

|   |       |      | 100: Rising edge 2.54V/falling edge 2.46V;                  |   |

|   |       |      | 101: Rising edge 2.72V/falling edge 2.63V;                  |   |

|   |       |      | 110: Rising edge 2.92V/falling edge 2.83V;                  |   |

|   |       |      | 111: Rising edge 3.10V/falling edge 3.01V.                  |   |

|   |       |      | Power supply voltage monitoring function enable flag bit:   |   |

| 4 | PVDE  | RW   | 1: Enable power supply voltage monitoring function;         | 0 |

|   |       |      | 0: Disable power supply voltage monitoring function.        |   |

|   |       |      | Clears the standby status flag bit and reads always 0.      |   |

| 3 | CSBF  | RW1  | 1: Setting 1 clears the SBF standby status flag bit;        | 0 |

|   |       |      | 0: Clear 0 is invalid.                                      |   |

|   |       |      | Clear the wake-up status flag bit, readout is always 0.     |   |

| 2 | OWNER | DIVI | 1: Clear the WUF flag bit after 2 system clock cycles after | 0 |

| 2 | CWUF  | RW1  | setting 1;                                                  | 0 |

|   |       |      | 0: Clearing 0 is invalid.                                   |   |

|   |       |      | Standby/shutdown mode selection bit for power-down deep     |   |

|   |       |      | sleep scenarios.                                            |   |

| 1 | PDDS  | RW   | 1: Enter Standby mode;                                      | 0 |

|   |       |      | 0: Enter Shutdown mode, voltage regulator state is          |   |

|   |       |      | controlled by LPDS.                                         |   |

|   |       |      | Voltage regulator operating mode selection bit in shutdown  |   |

| 0 | LDDG  |      | mode. PDDS=0, this bit is valid.                            | 0 |

| 0 | LPDS  | RW   | 1: The voltage regulator operates in low-power mode;        | 0 |

|   |       |      | 0: The voltage regulator operates in normal mode.           |   |

Note: Registers BIT16~BIT20 can only be reset by BACKUP, other BITs are reset when waking up from Standby mode.

### 2.4.2 Power Control/Status Register (PWR\_CSR)

| 31 | 30       | 29 | 28 | 27 | 26 | 25 | 24       | 23 | 22 | 21      | 20 | 19 | 18   | 17  | 16  |

|----|----------|----|----|----|----|----|----------|----|----|---------|----|----|------|-----|-----|

|    | Reserved |    |    |    |    |    |          |    |    |         |    |    |      |     |     |

| 15 | 14       | 13 | 12 | 11 | 10 | 9  | 8        | 7  | 6  | 5       | 4  | 3  | 2    | 1   | 0   |

|    | Reserved |    |    |    |    |    | EWU<br>P |    | F  | Reserve | d  |    | PVD0 | SBF | WUF |

| Bit    | Name     | Access | Description                                                                                                                                                                                                                            | Reset value |

|--------|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| [31:9] | Reserved | RO     | Reserved                                                                                                                                                                                                                               | 0           |

| 8      | EWUP     | RW     | <ul> <li>WKUP pin enable bit:</li> <li>1: WKUP is forced to be configured as an input pull-down state for waking up the MCU from standby;</li> <li>0: WKUP pin can be used for GPIOs with no wake-up from standby function.</li> </ul> | 0           |

| [7:3]  | Reserved | RO     | Reserved                                                                                                                                                                                                                               | 0           |

| 2      | PVD0     | RO     | PVD output status flag bit. This bit is valid when PVDE=1                                                                                                                                                                              | 0           |

|   |     |    | in the PWR_CTLR register.                                |   |  |

|---|-----|----|----------------------------------------------------------|---|--|

|   |     |    | 1: VDD and VDDA are below the PVD threshold set by       |   |  |

|   |     |    | PLS[2:0];                                                |   |  |

|   |     |    | 0: VDD and VDDA are above the PVD threshold set by       |   |  |

|   |     |    | PLS[2:0].                                                |   |  |

|   | SBF | RO | Standby status flag bit, which can be cleared by CSBF    | 0 |  |

| 1 |     |    | position 1.                                              |   |  |

| 1 |     |    | 1: MCU is in Standby mode;                               |   |  |

|   |     |    | 0: MCU is not in Standby mode.                           |   |  |

|   |     |    | Wake-up event status flag bit, which can be cleared by   |   |  |

|   |     |    | CWUF position 1.                                         |   |  |

| 0 | WUF | RO | 1: A wake-up event or RTC alarm event is detected at the | 0 |  |

|   |     |    | WKUP pin;                                                |   |  |

|   |     |    | 0: No wake-up event has occurred.                        |   |  |

Note: This register remains unchanged after waking up from Standby mode.

## Chapter 3 Reset and Clock Control (RCC)

The controller provides different forms of resets and configurable clock tree structures based on the division of power areas and peripheral power management considerations in the application. This section describes the scope of each clock in the system.

### **3.1 Main Features**

- Multiple reset forms

- Multiple clock sources, bus clock management

- Built-in external crystal oscillation monitoring and clock security system

- Independent management of each peripheral clock: Reset, On, Off

- Supports internal clock output

#### 3.2 Reset

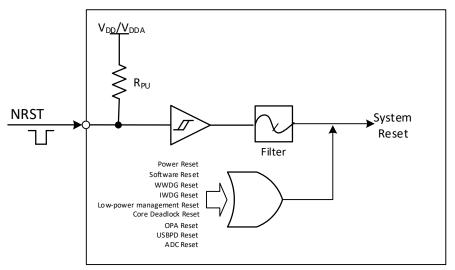

The controller provides 3 forms of reset: Power Reset, System Reset, and Backup Domain Reset.

#### 3.2.1 Power Reset

When a power reset occurs, all registers except the backup domain (which is powered by VBAT) will be reset.

The conditions for its production include:

- Power-on/power-off reset (POR/PDR reset)

- Wake-up from Standby mode

#### 3.2.2 System Reset

When a system reset occurs, all registers except the reset flag and the backup domain in the control / status register RCC\_RSTSCKR are reset. The source of the reset event is identified by looking at the reset status flag bit in the RCC\_RSTSCKR register.

The conditions for its production include:

- Low level signal on NRST pin (External reset)

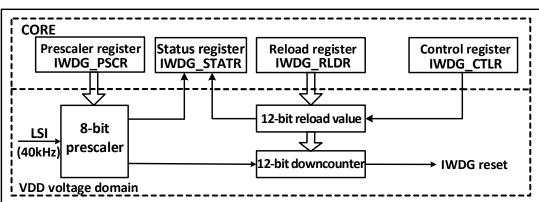

- Window watchdog count terminated (WWDG reset)

- Independent watchdog count terminated (IWDG reset)

- Software reset (SW reset)

- Low-power management reset

- Core deadlock reset

- OPA reset

- USBPD reset

- ADC reset

Window/independent watchdog reset: Triggered by window/independent watchdog peripheral timer count cycle overflow, see the corresponding chapter for a detailed description.

Software reset: This product resets the system through the SYSRST position 1 of the interrupt configuration register PFIC\_CFGR in the programmable interrupt controller PFIC or the RSTSYS position 1 of the configuration register PFIC SCTLR, refer to the corresponding chapter.

Low-power management reset: By setting the STANDY\_RST position 0 in the bytes selected by the user, the Standby mode reset will be enabled. After the process of entering the Standby mode is performed, the execution system is reset instead of entering the Standby mode. The Stop mode reset is enabled by setting the STOP\_RST position 0 in the byte selected by the user. At this time, after the process of entering the Stop mode is performed, the system will be reset instead of entering the Stop mode.

Core Deadlock Reset: when the LOCKUP of PFIC\_SCTLR register is 0, the kernel deadlock is enabled, and the kernel will go into deadlock when it executes exceptions and NMI executes instructions. When the LKUPEN bit of the EXTEN CTR register is enabled, the system will reset in case of a Lock-up condition.

OPA reset: When the OPA reset is enabled, the high level of the OPA output will cause an OPA reset.

USBPD Reset: When PD\_RST\_EN is 1, the CH32L103 supports the reset generated by the Hard Reset of the USBPD signal frame. If IE\_RX\_RESET is also 1, the Reset generated by Cable Reset of signal frames is also supported. USBPD does not have a reset flag, but the resulting reset effect is the same as a software reset.

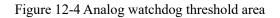

ADC reset: With the ADC Watchdog reset enabled, ADC reset occurs when ADC data is greater than the watchdog high threshold or less than the watchdog low threshold.

### 3.2.3 Backup Domain Reset

When a backup domain reset occurs, only the backup domain registers are reset, including the backup registers, the RCC\_BDCTLR registers (RTC enable and LSE oscillator). The conditions for its generation include:

- Caused by  $V_{DD}$  or  $V_{BAT}$  power-up with both  $V_{DD}$  and  $V_{BAT}$  powered down

- Set BDRST to 1 of the RCC\_BDCTLR register

- Set BKPRST to 1 of the RCC\_PB1PRSTR register

### 3.3 Clock

### 3.3.1 System Clock Structure

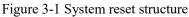

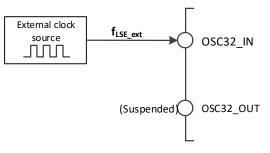

Figure 3-2 Clock tree block diagram

*Note: When using the USB function, the CPU frequency must be 48MHz, 72MHz or 96MHz. when the system wakes up from Stop or Standby mode, the system will automatically switch to HSI as the main frequency.*

#### 3.3.2 High-speed Clock (HIS/HSE)

HSI is a high-speed clock signal generated by the RC oscillator of 8MHz in the system. The HIS RC oscillator can

provide the system clock without any external devices. Its start-up time is very short, but the clock frequency accuracy is poor. The HSI is turned on and off by setting the HSION bit in the RCC\_CTLR register, and the HSIRDY bit indicates whether the HSIRC oscillator is stable. The system defaults to HSION and HSIRDY setting 1 (it is recommended that you do not turn it off). If the HSIRDYIE bit of the RCC\_INTR register is set, the corresponding interrupt will be generated.

- The HSI RC oscillator can enter HSILP position 1 into the internal low-power mode through the RCC\_CTRL register.

- Factory calibration: differences in manufacturing processes will lead to different RC oscillation frequencies of each chip, so HSI calibration is performed for each chip before it leaves the factory. After the system is reset, the factory calibration value is loaded into the HSICAL [7:0] in the RCC CTLR register.

- User adjustment: depending on the voltage or ambient temperature, the application can adjust the HSI frequency through the HSITRIM [4:0] bit in the RCC CTLR register.

Note: If the HSE crystal oscillator fails, the HSI clock will be used as a backup clock source (clock security system).

HSE is an external high-speed clock signal, including external crystal/ceramic resonator generation or external high-speed clock input.

HSE crystal oscillator can enter HSELP position 1 into low-power mode through the RCC\_CTRL register.

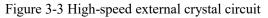

• External Crystal/Ceramic Resonator (HSE Crystal): An external 3-25MHz external oscillator provides a more accurate clock source for the system. Further information can be found in the Electrical Characteristics section of the datasheet. The HSE crystal can be turned on and off by setting the HSEON bit in the RCC\_CTLR register. The HSERDY bit indicates whether the HSE crystal oscillation is stable or not, and the hardware sends the clock into the system only after the HSERDY bit is set to one. If the HSERDYIE bit in the RCC\_INTR register is set, the appropriate interrupt will be generated.

Note: The load capacitance needs to be as close as possible to the oscillator pins and the capacitance value selected according to the crystal manufacturer's parameters.

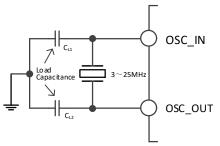

• External High Speed Clock Source (HSE Bypass): this mode feeds the clock source directly from the external source to the OSC\_IN pin, with the OSC\_OUT pin dangling. A maximum frequency of 25MHz is supported. The application program needs to set the HSEBYP bit to turn on the HSE bypass function with the HSEON bit at 0, and then set the HSEON bit again.

Figure 3-4 High-speed clock source circuit

#### 3.3.3 Low-speed Clock (LSI/LSE)

LSI is a low-speed clock signal generated by a RC oscillator of about 40KHz in the system. It can be kept running in both downtime and standby modes, providing clock references for RTC clocks, independent watchdogs, and wake-up units. For further information, please refer to the electrical characteristics section of the data manual. LSI can be turned on and off by setting the LSION bit in the RCC\_RSTSCKR register, and then check whether the LSIRC oscillation is stable by querying the LSIRDY bit, and the hardware sends the clock in after LSIRDY position 1. If the LSIRDYIE bit of the RCC INTR register is set, the corresponding interrupt will be generated.

LSE is an external low-speed clock signal, including external crystal/ceramic resonator generation or external low-speed clock input. It provides a low-power and accurate clock source for RTC clocks or other timing functions.

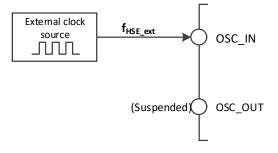

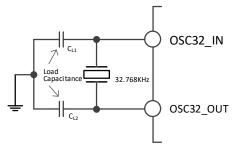

• External crystal/ceramic resonator (LSE crystal): External low-speed oscillator with external 32.768KHz. LSE is turned on and off by setting the LSEON bit in the RCC\_BDCTLR register, and the LSERDY bit indicates whether the LSE crystal oscillation is stable or not, and the hardware sends the clock into the system after LSERDY position 1. If the LSERDYIE bit of the RCC\_INTR register is set, the corresponding interrupt will be generated.

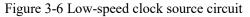

• External low-speed clock source (LSE bypass): this mode feeds the clock source directly from the outside to the OSC32\_IN pin, and the OSC32\_OUT pin is suspended. The application needs to set the LSEBYP bit when the LSEON bit is 0, turn on the LSE bypass function, and then set the LSEON bit.

#### 3.3.4 PLL Clock

By configuring the RCC\_CFGR0 register and the expansion register EXTEN\_CTR, the internal PLL clock can choose three clock sources and frequency doubling factors, which must be set before each PLL is turned on, and these parameters cannot be changed once the PLL is started. The PLLON bit in the set RCC\_CTLR register is turned on and off, the PLLRDY bit indicates whether the PLL clock is stable, and the hardware feeds the clock into the system after PLLRDY position 1. If the PLLRDYIE bit of the RCC\_INTR register is set, the corresponding interrupt will be generated.

PLL clock source:

- HSI clock feed

- HSI clock feed through 2-division frequency

- HSE clock feed

- HSE clock feed through 2-division frequency

#### **3.3.5 Bus/Peripheral Clock**

#### 3.3.5.1 System Clock (SYSCLK)

By configuring the RCC\_CFGR0 register SW[1:0] bit to configure the system clock source, SWS[1:0] indicates the current system clock source.

- HSI as the system clock.

- HSE as the system clock.

- PLL clock as the system clock.

After the controller is reset, the default HSI clock is selected as the system clock source. The switching between clock sources does not occur until the target clock source is ready.

#### 3.3.5.2 HB/PB1/PB2 Bus Peripheral Clock (HCLK/PCLK1/PCLK2)

HB (High Performance Bus), whose bus peripheral clock is HCLK; PB1 (Peripheral Bus 1), whose bus peripheral clock is PCLK1; and PB2 (Peripheral Bus 2), whose bus peripheral clock is PCLK2.

By configuring the HPRE [3:0], PPRE1 [2:0] and PPRE2 [2:0] bits of the RCC\_CFGR0 register, the clocks of the HB, PB1 and PB2 buses can be configured respectively. These bus clocks determine the peripheral interface mounted below them to access the clock reference. The application can adjust different values to reduce the power consumption of some peripherals.

Different peripheral modules can be reset and restored to the initial state through each bit in the RCC\_HBRSTR, RCC\_PB1PRSTR and RCC\_PB2PRSTR registers.

The communication clock interface of different peripheral modules can be turned on or off separately through each bit in the RCC\_HBPCENR, RCC\_PB1PCENR and RCC\_PB2PCENR registers. When using a peripheral, you first need to turn on its clock enable bit before you can access its register.

#### 3.3.5.3 RTC Clock (RTCCLK)

By setting the RTCSEL[1:0] bit of the RCC\_BDCTLR register, the RTCCLK clock source can be provided by the HSE/128, LSE, or LSI clock. Before modifying this bit, make sure that the DBP position 1 in the power control register (PWR\_CTLR) can be reset only if the backup domain is reset.

- LSE acts as the RTC clock: Since LSE is powered by V<sub>BAT</sub> in the backup domain, RTC continues to work as long as V<sub>BAT</sub> maintains power, even though V<sub>DD</sub> power is cut off.

- LSI as the RTC clock: If the V<sub>DD</sub> power is cut off, RTC automatic wake up is not guaranteed.

- HSE/128 acts as the RTC clock: If the V<sub>DD</sub> power supply is cut off or the internal voltage regulator is turned off (the power supply in the 1.8V domain is cut off), the RTC state is uncertain.

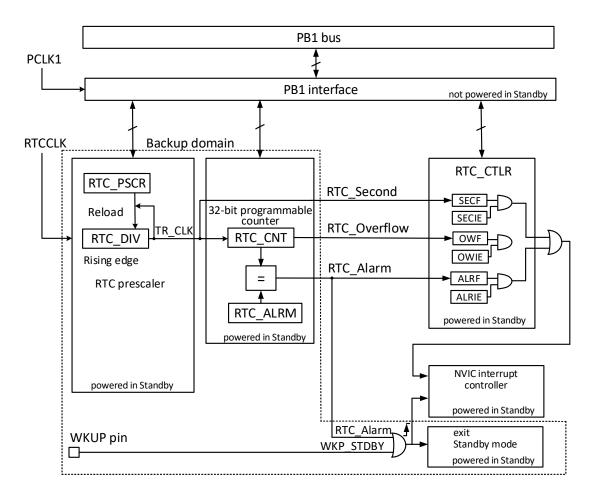

#### 3.3.5.4 Independent Watchdog Clock

If the independent watchdog has been started by the hardware configuration or software, the LSI oscillator will be forced to open and cannot be turned off. After the LSI oscillator is stabilized, the clock is supplied to the IWDG.

#### 3.3.5.5 Microcontroller Clock Output (MCO)

The microcontroller allows clock signals to be output to MCO pins. The alternate push-pull output mode is configured in the corresponding GPIO port register. by configuring the RCC\_CFGR0 register MCO [2:0] bit, the following 4 clock signals can be selected as MCO clock output:

- System clock (SYSCLK) output.

- HSI clock output.

- HSE clock output.

- PLL clock output through 2 frequency division

#### 3.3.5.6 USB Clock

The USB 48MHz clock source comes from the PLL clock through a configurable frequency divider, where PLL supports three clock configurations, including 48MHz, 72MHz and 96MHz, and outputs the 48MHz clock to USBFS through the USBPRE [1:0] bit of the configuration register RCC\_CFGR0.

#### 3.3.5.7 ADC Clock

ADC can select the input clock source and control the duty cycle of the ADC clock through the RCC\_CFGR0 register.

The ADC\_PRE\_ADJ bit is used to select the input clock in clock configuration register 0, and when the position 1, the ADC input clock selects the HCLK clock input. When the position is 0, the ADC input clock selects the clock input of the PLCK2 after ADC frequency division (ADCPRE [1:0]), and the duty cycle of the ADC clock can be changed through the corresponding configuration of the ADC\_DUTY\_CHG bit.

#### 3.3.6 Clock Security System

The clock security system is a running protection mechanism of the controller, which can switch to the HSI clock in the case of HSE clock transmission failure, and generate interrupt notification, allowing application software to complete the rescue operation.

Activate the clock security system by setting CSSON position 1 of the RCC\_CTLR register. At this point, the clock monitor will be enabled after the HSE oscillator startup (HSERDY=1) delay and turned off after the HSE clock is turned off. Once the HSE clock fails during the operation of the system, the HSE oscillator will be turned off, the clock failure event will be sent to the brake input of the advanced timer (TIM1), and the clock security interrupt will be generated, CSSF position 1, and the application will enter the NMI unshielded interrupt. By setting the CSSC bit, the CSSF bit flag can be cleared and the NMI interrupt suspension bit can be revoked.

If the current HSE is the system clock, or the current HSE is the PLL input clock and the PLL is the system clock, the clock security system will automatically switch the system clock to the HSI oscillator and turn off the HSE oscillator and PLL in the event of a HSE failure.

### **3.4 Register Description**

| Table 3-1 | RCC-related | registers list |  |

|-----------|-------------|----------------|--|

| 14010 5-1 | RCC-Iclated | registers fist |  |

| Name             | Access address | Description                          | Reset value |

|------------------|----------------|--------------------------------------|-------------|

| R32_RCC_CTLR     | 0x40021000     | Clock control register               | 0x0000xx83  |

| R32_RCC_CFGR0    | 0x40021004     | Clock configuration register 0       | 0x00000000  |

| R32_RCC_INTR     | 0x40021008     | Clock interrupt register             | 0x00000000  |

| R32_RCC_PB2PRSTR | 0x4002100C     | PB2 peripheral reset register        | 0x00000000  |

| R32_RCC_PB1PRSTR | 0x40021010     | PB1 peripheral reset register        | 0x00000000  |

| R32_RCC_HBPCENR  | 0x40021014     | HB peripheral clock enable register  | 0x00000014  |

| R32_RCC_PB2PCENR | 0x40021018     | PB2 peripheral clock enable register | 0x00000000  |

| R32_RCC_PB1PCENR | 0x4002101C     | PB1 peripheral clock enable register | 0x00000000  |

| R32_RCC_BDCTLR   | 0x40021020     | Backup domain control register       | 0x00000000  |

| R32_RCC_RSTSCKR  | 0x40021024     | Control/status register              | 0x0C000000  |

| R32_RCC_HBRSTR   | 0x40021028     | HB peripheral reset register         | 0x00000000  |

#### 3.4.1 Clock Control Register (RCC\_CTLR)

| 31          | 30 | 29   | 28    | 27 | 26 | 25         | 24        | 23        | 22     | 21    | 20         | 19    | 18         | 17         | 16    |

|-------------|----|------|-------|----|----|------------|-----------|-----------|--------|-------|------------|-------|------------|------------|-------|

|             |    | Rese | erved |    |    | PLL<br>RDY | PLL<br>ON | R         | eserve | ed    | HSELP      | CSSON | HSE<br>BYP | HSE<br>RDY | HSEON |

| 15          | 14 | 13   | 12    | 11 | 10 | 9          | 8         | 7         | 6      | 5     | 4          | 3     | 2          | 1          | 0     |

| HSICAL[7:0] |    |      |       |    |    |            | HSIT      | [RIM[4:0] |        | HSILP | HSI<br>RDY | HSION |            |            |       |

| Bit     | Name     | Access | Description                                                                                                                                                             | Reset value |

|---------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| [31:26] | Reserved | RO     | Reserved                                                                                                                                                                | 0           |

| 25      | PLLRDY   | RO     | PLL clock ready flag (set by hardware):<br>1: PLL locked;<br>0: PLL unlocked                                                                                            | 0           |

| 24      | PLLON    |        | <ul> <li>PLL enable:</li> <li>1: Enable PLL clock;</li> <li>0: Disable PLL clock.</li> <li>Note: Cleared by hardware when entering Stop or<br/>Standby mode.</li> </ul> | 0           |

| [23:21] | Reserved | RO     | Reserved                                                                                                                                                                | 0           |

| 20      | HSELP    | RW     | HSE low-power mode:<br>1: On;<br>0: Off.                                                                                                                                | 1           |

| r      |              |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

|--------|--------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 19     | CSSON        | RW | Clock security system enable:<br>1: Enable clock security system. When HSE is ready<br>(HSERDY is set to 1), the hardware turns on the clock<br>monitoring function for HSE and finds that HSE<br>abnormal triggers the CSSF flag and NMI interrupt;<br>when HSE is not ready, the hardware turns off the clock<br>monitoring function for HSE.<br>0: Disable clock security system.                                                                                   | 0      |

| 18     | HSEBYP       | RW | <ul> <li>External high-speed clock bypass:</li> <li>1: Bypass the external high-speed crystal/ceramic resonator (if the HSEON bit is 0, set the HSEBYP bit to turn on the HSE bypass function, and then set the HSEON bit again to take effect);</li> <li>0: No bypass high-speed external crystal/ceramic resonator.</li> </ul>                                                                                                                                       | 0      |

| 17     | HSERDY       | RO | <ul> <li>External high-speed crystal oscillation stability ready flag (set by hardware):</li> <li>1: External high-speed crystal oscillation is stable.</li> <li>0: External high-speed crystal oscillation is not stable.</li> <li><i>Note: After the HSEON bit is cleared, it needs 6 HSE cycles to clear 0.</i></li> </ul>                                                                                                                                          | 0      |

| 16     | HSEON        | RW | <ul> <li>HSE clock enable:</li> <li>1: Enable HSE oscillator;</li> <li>0: Disable HSE oscillator.</li> <li>Note: Clear by hardware to stop HSE oscillator when entering Stop or Standby mode.</li> </ul>                                                                                                                                                                                                                                                               | 0      |

| [15:8] | HSICAL[7:0]  | RO | Internal high-speed clock calibration value<br>These bits are automatically initialized at system startup.                                                                                                                                                                                                                                                                                                                                                             | xxh    |

| [7:3]  | HSITRIM[4:0] | RW | Internal high-speed clock adjustment:<br>The user can enter an adjustment value that is<br>superimposed on the HSICAL [7:0] value to adjust the<br>frequency of the internal HSIRC oscillator according to<br>changes in voltage and temperature.<br>The default value is 16, which can adjust the HSI to<br>$8MHz \pm 1\%$ ; the change of HSICAL is adjusted about<br>20KHz per step when LP=0. The change of HSICAL is<br>adjusted about 2.5KHz per step when LP=1. | 10000Ь |

| 2      | HSILP        | RW | HIS internal low-power mode:<br>1: On, the HSI frequency is reduced to 1MHz.<br>0: Off<br>Note: The HSI enters the internal low-power mode by<br>loading the value of the 0x1FFFF72A address into<br>HSITRIM[4:0] to realize the correction in the low-power<br>mode                                                                                                                                                                                                   | 0      |

| 1 | HSIRDY | RO | Internal high-speed HSI stable ready flag (set by<br>hardware)<br>1: Internal high-speed HSI is stable;<br>0 Internal high-speed HSI is not stable.<br><i>Note: After the HSION bit is cleared, it needs 6 HSI cycles to clear 0.</i>                                                                                                                  | 1 |

|---|--------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 0 | HSION  | RW | Internal high-speed clock HSI enable control bit:<br>1: Enable the HSI oscillator;<br>0: Disable the HSI oscillator.<br><i>Note: This bit is set by hardware to 1 to start the internal</i><br><i>HSI oscillator when returning from standby and stop</i><br><i>mode or when the external oscillator HSE used as the</i><br><i>system clock fails.</i> | 1 |

# **3.4.2 Clock Configuration Register 0 (RCC\_CFGR0)** Offset address: 0x04

| 31              | 30    | 29         | 28      | 27           | 26 | 25     | 24  | 23 | 22         | 21              | 20   | 19      | 18    | 17               | 16         |

|-----------------|-------|------------|---------|--------------|----|--------|-----|----|------------|-----------------|------|---------|-------|------------------|------------|

| ADC_P<br>RE_ADJ |       | C_DU'<br>G | ГҮ_СН   | Reser<br>ved | N  | ICO[2: | 0]  |    | PRE<br>:0] |                 | PLLM | JL[3:0] |       | PLL<br>XTP<br>RE | PLL<br>SRC |

| 15              | 14    | 13         | 12      | 11           | 10 | 9      | 8   | 7  | 6          | 5               | 4    | 3       | 2     | 1                | 0          |

| ADCPRI<br>]     | E[1:0 | P          | PRE2[2: | 0]           | PP | RE1[2  | :0] |    | HPRI       | E[ <b>3:0</b> ] |      | SWS     | [1:0] | SW               | [1:0]      |

| Bit     | Name             | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Reset value |

|---------|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 31      | ADC_PRE_ADJ      | RW     | <ul><li>ADC input clock selection:</li><li>1: Select the HCLK clock input;</li><li>0: Select the PLCK2 clock input after ADC division (ADCPRE[1:0]).</li></ul>                                                                                                                                                                                                                                                                                                                    | 0           |

| [30:28] | ADC_DUTY_C<br>HG | RW     | ADC clock duty cycle control bit:<br>000: High level duration is half of ADC clock cycle.<br>001: High level duration adds 1 HCLK clock cycle.<br>010: High level duration adds 2 HCLK clock cycles.<br>011: High level duration adds 3 HCLK clock cycles.<br>100: High level duration adds 4 HCLK clock cycles.<br>101: High level duration adds 5 HCLK clock cycles.<br>110: High level duration adds 6 HCLK clock cycles.<br>111: High level duration adds 7 HCLK clock cycles | 000         |

| 27      | Reserved         | RO     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0           |

| [26:24] | MCO[2:0]         | RW     | Microcontroller MCO pin clock output control:<br>0xx: No clock output.<br>100: System clock (SYSCLK) output.<br>101: Internal oscillator clock (HSI) output.<br>110: External oscillator clock (HSE) output.                                                                                                                                                                                                                                                                      | 000Ь        |

|             |             |       | 111: PLL clock output after 2 frequency division            |        |  |

|-------------|-------------|-------|-------------------------------------------------------------|--------|--|

|             |             |       | USB clock division frequency configuration:                 |        |  |

|             |             |       | 00: 1-division frequency (for PLLCLK=48MHz);                |        |  |

| [23:22]     | USBPRE[1:0] | RW    | 01: 2-division frequency (for PLLCLK=96MHz);                | 00b    |  |

|             |             |       | 10: 1.5-division frequency (for PLLCLK=72MHz);              |        |  |

|             |             |       | 11: Reserved.                                               |        |  |

|             |             |       | PLL clock multiplication factor (not writable until PLL is  |        |  |

|             |             |       | off):                                                       |        |  |

|             |             |       | 0000: PLL 2x output; 0001: PLL 3x output;                   |        |  |

|             |             |       | 0010: PLL 4x output; 0011: PLL 5x output;                   |        |  |

| [21.10]     |             | RW    | 0100: PLL 6x output; 0101: PLL 7x output;                   | 00001- |  |

| [21:18]     | PLLMUL[3:0] | ĸw    | 0110: PLL 8x output; 0111: PLL 9x output;                   | 0000b  |  |

|             |             |       | 1000: PLL 10x output; 1001: PLL 11x output;                 |        |  |

|             |             |       | 1010: PLL 12x output; 1011: PLL 13x output;                 |        |  |

|             |             |       | 1100: PLL 14x output; 1101: PLL 15x output;                 |        |  |

|             |             |       | 1110: PLL 16x output; 1111: PLL 18x output.                 |        |  |

|             |             |       | HSE split frequency feed to PLL control (write only when    |        |  |

| 17 PLLXTPRE | DIIVTDDE    | RW    | PLL is off):                                                | 0      |  |

|             | FLLAIFKL    | K W   | 1: HSE 2-division frequency feed to PLL;                    | 0      |  |

|             |             |       | 0: HSE no-division feed to PLL.                             |        |  |

|             |             |       | Input clock source to the PLL (not writable until the PLL   |        |  |

|             |             |       | is turned off):                                             |        |  |

| 16          | PLLSRC      | RW    | 1: HSE undivided or 2-division fed to the PLL;              | 0      |  |

| 10          | I LLSKC     | 17.14 | 0: HSI undivided or 2-division fed to the PLL.              | Ŭ      |  |

|             |             |       | Note: The division of the HSI clock is controlled using the |        |  |

|             |             |       | EXTEN_CTR register HSIPRE bit.                              |        |  |

|             |             |       | ADC clock source pre-divided frequency control:             |        |  |

|             |             |       | 00: PCLK2 2-division frequency as ADC clock;                |        |  |

| [15:14]     | ADCPRE[1:0] | RW    | 01: PCLK2 4-division frequency as ADC clock;                | 00b    |  |

| [13.11]     |             | 1     | 10: PCLK2 6-division frequency as ADC clock;                | 000    |  |

|             |             |       | 11: PCLK2 8-division frequency as ADC clock.                |        |  |

|             |             |       | Note: The ADC clock should not exceed 48MHz maximum.        |        |  |

|             |             |       | PB2 clock source pre-divided control:                       |        |  |

|             |             |       | 0xx: HCLK no frequency division;                            |        |  |

| [13:11]     | PPRE2[2:0]  | RW    | 100: HCLK 2-division frequency;                             | 000b   |  |

| []          | []          |       | 101: HCLK 4-division frequency;                             |        |  |

|             |             |       | 110: HCLK 8-division frequency;                             |        |  |

|             |             |       | 111: HCLK 16-division frequency.                            |        |  |

|             |             |       | PB1 clock source pre-divided control:                       |        |  |

|             |             |       | 0xx: HCLK no frequency division;                            |        |  |

| [10:8]      | PPRE1[2:0]  | RW    | 100: HCLK 2-division frequency;                             | 000b   |  |

| [10.8]      | 11 KE1[2.0] | 17.44 | 101: HCLK 4-division frequency;                             |        |  |

|             |             |       | 110: HCLK 8-division frequency;                             |        |  |

|             |             |       | 111: HCLK 16-division frequency.                            |        |  |

| i     |           | r  | 1                                                          |       |

|-------|-----------|----|------------------------------------------------------------|-------|

|       |           |    | HB clock source pre-divided control:                       |       |

|       |           |    | 0xxx: SYSCLK no frequency division;                        |       |

|       |           |    | 1000: SYSCLK 2-division frequency;                         |       |

|       |           |    | 1001: SYSCLK 4-division frequency;                         |       |

| [7.4] |           | RW | 1010: SYSCLK 8-division frequency;                         | 0000b |

| [7:4] | HPRE[3:0] | ΚW | 1011: SYSCLK 16-division frequency;                        | 00000 |

|       |           |    | 1100: SYSCLK 64-division frequency;                        |       |

|       |           |    | 1101: SYSCLK 128-division frequency;                       |       |

|       |           |    | 1110: SYSCLK 256-division frequency;                       |       |

|       |           |    | 1111: SYSCLK 512-division frequency.                       |       |

|       |           |    | System clock (SYSCLK) status (set by hardware):            |       |

|       |           |    | 00: System clock source is HSI;                            |       |

| [3:2] | SWS[1:0]  | RO | 01: System clock source is HSE;                            | 00b   |

|       |           |    | 10: System clock source is PLL;                            |       |

|       |           |    | 11: Not available.                                         |       |

|       |           |    | Select the system clock source:                            |       |

|       |           |    | 00: HSI as system clock;                                   |       |

|       |           |    | 01: HSE as system clock;                                   |       |

|       |           |    | 10: PLL output as system clock;                            |       |

| [1:0] | SW[1:0]   | RW | 11: not available.                                         | 00b   |

|       |           |    | Note: With Clock Safe System enabled (CSSON=1), the        |       |

|       |           |    | selection of HSI as the system clock is forced by hardware |       |

|       |           |    | when returning from Standby and Stop mode or when the      |       |

|       |           |    | external oscillator HSE used as the system clock fails.    |       |

### 3.4.3 Clock Interrupt Register (RCC\_INTR)

| 31 | 30                                                                           | 29   | 28    | 27 | 26 | 25   | 24   | 23    | 22              | 21              | 20              | 19              | 18              | 17              | 16 |

|----|------------------------------------------------------------------------------|------|-------|----|----|------|------|-------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----|

|    |                                                                              | Rese | erved |    |    | CSSC | Rese | erved | PLL<br>RDY<br>C | HSE<br>RDY<br>C | HSI<br>RDY<br>C | LSE<br>RDY<br>C | LSI<br>RDY<br>C |                 |    |

| 15 | 14                                                                           | 13   | 12    | 11 | 10 | 9    | 8    | 7     | 6               | 5               | 4               | 3               | 2               | 1               | 0  |

| F  | Reserved PLL HSE HSI LSE LSI<br>RDYI RDYI RDYI RDYI RDYI RDYI<br>E E E E E E |      |       |    |    |      | CSSF | Rese  | erved           | PLL<br>RDY<br>F | HSE<br>RDY<br>F | HSI<br>RDY<br>F | LSE<br>RDY<br>F | LSI<br>RDY<br>F |    |

| Bit     | Name     | Access | Description                                                                                          | Reset value |

|---------|----------|--------|------------------------------------------------------------------------------------------------------|-------------|

| [31:24] | Reserved | RO     | Reserved                                                                                             | 0           |

| 23      | CSSC     | WO     | Clear clock security system interrupt flag (CSSF):<br>1: Clear CSSF interrupt flag;<br>0: No effect. | 0           |

| [22:21] | Reserved | RO     | Reserved                                                                                             | 0           |

| 20      | PLLRDYC  | WO     | Clear PLL ready interrupt flag:<br>1: Clear PLLRDYF interrupt flag;                                  | 0           |

|         |          |    | 0: No effect.                                               |   |

|---------|----------|----|-------------------------------------------------------------|---|

|         |          |    | Clear HSE oscillator ready interrupt flag:                  |   |

| 19      | HSERDYC  | WO | 1: Clear HSERDYF interrupt flag;                            | 0 |

|         |          |    | 0: No effect.                                               |   |

|         |          |    | Clear HSI oscillator ready interrupt flag:                  |   |

| 18      | HSIRDYC  | WO | 1: Clear HSIRDYF interrupt flag;                            | 0 |

|         |          |    | 0: No effect.                                               |   |

|         |          |    | Clear LSE oscillator ready interrupt flag:                  |   |

| 17      | LSERDYC  | WO | 1: Clear LSERDYF interrupt flag;                            | 0 |

|         |          |    | 0: No effect.                                               |   |

|         |          |    | Clear LSI oscillator ready interrupt flag:                  |   |

| 16      | LSIRDYC  | WO | 1: Clear LSIRDYF interrupt flag;                            | 0 |

|         |          |    | 0: No effect.                                               |   |

| [15:13] | Reserved | RO | Reserved                                                    | 0 |

|         |          |    | PLL ready interrupt enable:                                 |   |

| 12      | PLLRDYIE | RW | 1: Enable PLL ready interrupt;                              | 0 |

|         |          |    | 0: Disable PLL ready interrupt.                             |   |

|         |          |    | HSE ready interrupt enable:                                 |   |

| 11      | HSERDYIE | RW | 1: Enable HSE ready interrupt;                              | 0 |

|         |          |    | 0: Disable HSE ready interrupt.                             |   |

|         |          |    | HSI ready interrupt enable:                                 |   |

| 10      | HSIRDYIE | RW | 1: Enable HSI ready interrupt;                              | 0 |

|         |          |    | 0: Disable HSI ready interrupt.                             |   |

|         |          |    | LSE ready interrupt enable:                                 |   |

| 9       | LSERDYIE | RW | 1: Enable LSE ready interrupt;                              | 0 |

|         |          |    | 0: Disable LSE ready interrupt.                             |   |

|         |          |    | LSI ready interrupt enable:                                 |   |

| 8       | LSIRDYIE | RW | 1: Enable LSI ready interrupt;                              | 0 |

|         |          |    | 0: Disable LSI ready interrupt.                             |   |

|         |          |    | Clock security system interrupt flag bit:                   |   |

|         |          |    | 1: HSE clock failure, resulting in clock security interrupt |   |

| 7       | CSSF     | RO | CSSI.                                                       | 0 |

|         |          |    | 0: no clock security system interrupt.                      |   |

|         |          |    | Set by hardware, clear when software write CSSC bit 1.      |   |

| [6:5]   | Reserved | RO | Reserved                                                    | 0 |

|         |          |    | PLL clock ready lock interrupt flag:                        |   |

|         |          |    | 1: PLL clock lock generates an interrupt;                   |   |

| 4       | PLLRDYF  | RO | 0: No PLL clock lock interrupt.                             | 0 |

|         |          |    | Set by hardware, clear when software write PLLRDYC          |   |

|         |          |    | bit 1.                                                      |   |

|         |          |    | HSE clock ready interrupt flag:                             |   |

| 2       | USEDDVE  |    | 1: HSE clock ready generates an interrupt;                  | 0 |