# 7-port USB HUB Controller Chip CH338

Datasheet Version: V1.1 https://wch-ic.com

#### 1. Overview

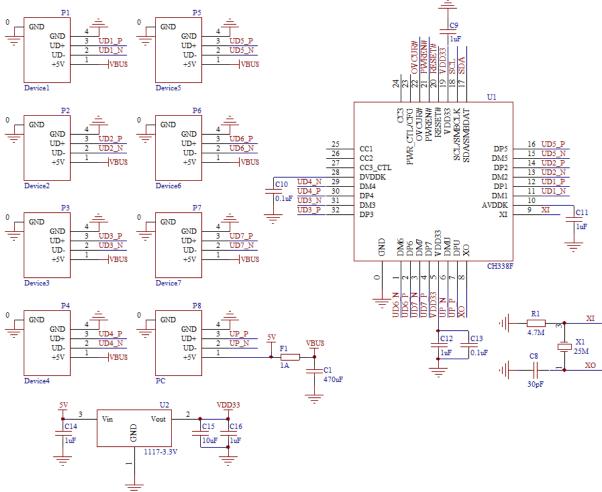

CH338 is a 7-port USB HUB controller chip that complies with the USB2.0 protocol specification. The upstream port supports USB2.0 high-speed and full-speed, the downstream port supports USB2.0 high-speed 480Mbps, full-speed 12Mbps and low-speed 1.5Mbps. It not only supports the low-cost STT mode (A single TT schedules 7 downstream ports in a time-sharing manner), but also supports the high-performance MTT mode (7 TTs each correspond to one port and are processed concurrently). In addition to the HUB controller function, some models also support PD function.

Industrial-grade design, streamlined peripherals, can be applied to computer and industrial computer motherboards, peripherals, embedded systems, etc.

The figure below is the system block diagram of CH338.

Type-C **SMBUS** I2C PD **USPORT Transceiver** UTMI **LED Controller USPORT Routing Logic** HS FS/LS REPEATER REPEATER **HUB Controller** TT\*7 **ROM DSPORT Routing Logic** DSPORT1 DSPORT4 DSPORT2 DSPORT3 DSPORT5 DSPORT6 DSPORT7 Transceiver Transceiver Transceiver Transceiver Transceiver Transceiver Transceiver

Figure 1-1 System block diagram

The figure above is the internal structure block diagram of the HUB controller system. HUB controller mainly includes three modules: Repeater, TT and controller. The controller is similar to an MCU processor and is used for global management and control. When the speed of the upstream port and the downstream port are consistent, the routing logic will connect the port to the Repeater. When the speed of the upstream port and the downstream port are inconsistent, the routing logic will connect the port to the TT.

TT is divided into two types: single TT and multiple TT, namely STT and MTT. STT is a time-sharing scheduling of a single TT core to process transactions sent by the USB host to all downstream ports. MTT refers to multiple TT parallel, which are seven TT cores respectively. Corresponding to and processing the transactions of a downstream port in real time, MTT can provide full bandwidth for the access equipment of each downstream port and better support the concurrent transmission of large amounts of data across multiple ports.

USPORT Transceiver: Upstream port transceiver PHY; DSPORT Transceiver: Downstream port transceiver PHY;

REPEATER: HUB repeater; TT: Handle converters.

#### 2. Feature

Note:

- 7-port USB HUB with 7 USB2.0 downstream ports, backward compatible with USB1.1 protocol specification

- Support independent power control for each port or GANG overall linkage power control

- Support independent over-current detection for each port or GANG overall over-current detection

- Support high-performance MTT mode, providing independent TT for each port to achieve full bandwidth concurrent transmission, the total bandwidth is 7 times that of STT

- Support port status LED indicator

- Whether to support composite devices, non-removable devices, custom VID, PID, port configuration and USB vender, product, serial number string descriptors, etc. can be configured through external EEPROM or internal EEPROM.

- Chip related parameters can be configured through the SMBus interface

- Built-in information memory, vender or product information and configuration can be customized in batches according to special needs of the industry

- Self-developed dedicated USBPHY, low-power consumption technology, supports self-power supply or bus power supply

- Functions such as self-powered or bus-powered modes can be configured through I/O pins

- Provide crystal oscillator, built-in capacitor, supports external clock input, built-in PLL provides 480MHz clock for USBPHY

- Some applications can support crystal-free mode, saving external crystals and capacitors.

- The upstream port has a built-in  $1.5K\Omega$  pull-up resistor, and the downstream port has a built-in pull-down resistor required by the USB Host, simplifying the peripherals.

- Some models have a built-in LDO linear step-down regulator, which can convert the USB bus power supply voltage into the chip's 3.3V working power supply.

- USB interface pins have 6KV Enhanced ESD Performance, Class 3A

- Industrial-grade temperature range: -40 to 85°C

- Available in QFN64, LQFP48, QFN32 and other small, low-cost, easy-to-process packages

Model

Function

CH338X

CH338L

CH338F

TT mode

MTT

MTT

MTT

Overcurrent detection

Independent/GANG

GANG mode

GANG mode

Table 1-1 Comparison of functions of models in the same cluster

| Power control             | Independent /GANG | GANG mode               | GANG mode   |  |

|---------------------------|-------------------|-------------------------|-------------|--|

| LED                       | 7+4               | 15                      | ×           |  |

| I/O pin configuration     |                   | ×                       | ×           |  |

| power supply mode         | V                 | ^                       | ^           |  |

| I/0 pin configuration     | ما                | ما                      | ×           |  |

| non-removable device      | V                 | V                       | ^           |  |

| External/internal         |                   |                         |             |  |

| EEPROM provide            | $\sqrt{}$         | $\sqrt{}$               | $\sqrt{}$   |  |

| configuration information |                   |                         |             |  |

| SMBus interface           | ٦/                | ما                      | 1           |  |

| configuration information | V                 | V                       | V           |  |

| Custom configuration      | ٦/                | ما                      | 1           |  |

| information               | V                 | V                       | <b>V</b>    |  |

| Upstream port switching   | ×                 | ×                       |             |  |

| function                  | ^                 | ^                       | V           |  |

| Extension/isolation       | ×                 | ×                       | 3/          |  |

| function                  | ^                 | ^                       | ٧           |  |

| Type-C / PD               | ×                 | ×                       | √           |  |

| Chin novyor cumply        | Single 3.3V       | Single 3.3V Single 3.3V |             |  |

| Chip power supply         | Siligie 3.3 v     | Or single 5V            | Single 3.3V |  |

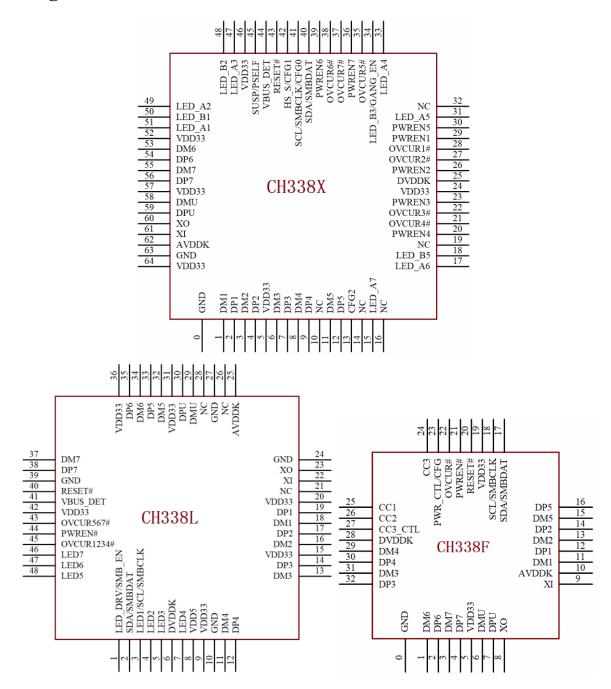

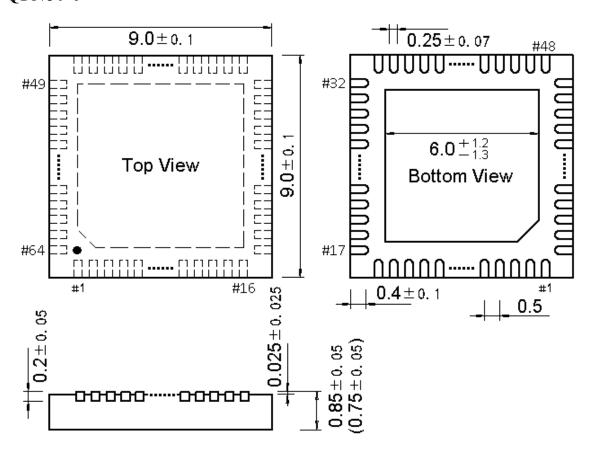

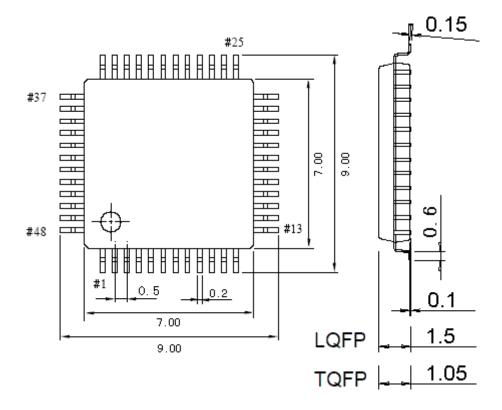

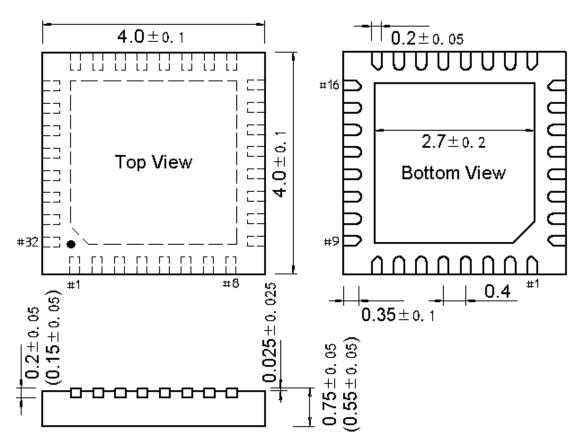

# 3. Package

Table 3-1 Package description

| Package form | Body size | Pin pitch     |         | Package description        | Order model |

|--------------|-----------|---------------|---------|----------------------------|-------------|

| QFN64×9      | 9*9mm     | 0.5mm 19.7mil |         | Quad Flat No-Lead Package  | CH338X      |

| LQFP48       | 7*7mm     | 0.5mm         | 19.7mil | Low Profile Quad Flat Pack | CH338L      |

| QFN32        | 4*4mm     | 0.4mm         | 15.7mil | Quad Flat No-Lead Package  | CH338F      |

Note: CH338F is preferred for small size; CH338X and CH338L focus on PCB compatibility.

Pin 0# is the EPAD of the QFN package and is a required connection.

# 4. Pin

Table 4-1 Pin definition

| Pin number (please refer to the pin |                     |        |                              |                     |                                                                                                                                     |

|-------------------------------------|---------------------|--------|------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| with                                | with the same name) |        | Pin name                     | Type <sup>(1)</sup> | Function description                                                                                                                |

| CH338X                              | CH338L              | CH338F |                              |                     |                                                                                                                                     |

| 58                                  | 29                  | 6      | DMU                          | USB                 | Upstream port USB2.0 signal line D-                                                                                                 |

| 59                                  | 30                  | 7      | DPU                          | USB                 | Upstream port USB2.0 signal line D+                                                                                                 |

| 1                                   | 18                  | 11     | DM1                          | USB                 | 1# Downstream port USB signal line D-                                                                                               |

| 2                                   | 19                  | 12     | DP1                          | USB                 | 1# Downstream port USB signal line D+                                                                                               |

| 3                                   | 16                  | 13     | DM2                          | USB                 | 2# Downstream port USB signal line D-                                                                                               |

| 4                                   | 17                  | 14     | DP2                          | USB                 | 2# Downstream port USB signal line D+                                                                                               |

| 6                                   | 13                  | 31     | DM3                          | USB                 | 3# Downstream port USB signal line D-                                                                                               |

| 7                                   | 14                  | 32     | DP3                          | USB                 | 3# Downstream port USB signal line D+                                                                                               |

| 8                                   | 11                  | 29     | DM4                          | USB                 | 4# Downstream port USB signal line D-                                                                                               |

| 9                                   | 12                  | 30     | DP4                          | USB                 | 4# Downstream port USB signal line D+                                                                                               |

| 11                                  | 32                  | 15     | DM5                          | USB                 | 5# Downstream port USB signal line D-                                                                                               |

| 12                                  | 33                  | 16     | DP5                          | USB                 | 5# Downstream port USB signal line D+                                                                                               |

| 53                                  | 34                  | 1      | DM6                          | USB                 | 6# Downstream port USB signal line D-                                                                                               |

| 54                                  | 35                  | 2      | DP6                          | USB                 | 6# Downstream port USB signal line D+                                                                                               |

| 55                                  | 37                  | 3      | DM7                          | USB                 | 7# Downstream port USB signal line D-                                                                                               |

| 56                                  | 38                  | 4      | DP7                          | USB                 | 7# Downstream port USB signal line D+                                                                                               |

| 61                                  | 22                  | 9      | XI                           | I                   | Crystal oscillator input terminal, connected to one terminal of the external crystal                                                |

| 60                                  | 23                  | 8      | XO                           | О                   | The inverting output terminal of the crystal oscillator is connected to the other terminal of the external crystal.                 |

| 43                                  | 40                  | 20     | RESET#                       | 51                  | External reset input, built-in pull-up resistor, active at low level, recommended to be left completely unconnected when not in use |

| -                                   | 8                   | -      | $ m V_{DD5}$                 | P                   | LDO power input, 5V or 3.3V, external 1uF or larger capacitor                                                                       |

| -                                   | 9                   | -      | $ m V_{DD33}$                | P                   | LDO power output, 3.3V, external 1uF or larger capacitor                                                                            |

| 5、57                                | 20、36               | 5、19   | $V_{DD33}$                   | P                   | Analog power input, 3.3V, external 1uF decoupling capacitor                                                                         |

| 52、64                               | 15、31               | -      | $V_{\mathrm{DD33}}$          | P                   | Auxiliary power input, 3.3V, external 1uF or 0.1uF decoupling capacitor                                                             |

| 24、46                               | 42                  | -      | $V_{\mathrm{DD33}}$          | P                   | I/O power input, 3.3V, external 1uF or 0.1uF decoupling capacitor                                                                   |

| 62                                  | 25                  | 10     | $AV_{DDK}$                   | P                   | 1.2V core power, external 1uF or 0.1uF decoupling capacitor                                                                         |

| 25                                  | 6                   | 28     | $\mathrm{DV}_{\mathrm{DDK}}$ | P                   | 1.2V core power, external 0.1uF decoupling capacitor                                                                                |

| 0                                   | 10、24               | 0      | GND                          | P                   | Common ground terminal, must be connected to GND                                                                                    |

| 63                                  | 27、39               | -      | GND                          | P                   | Common ground, optional connection                                                                                                  |

| 28 | -  | -  | OVCUR1#         | 5I | Downstream port 1 overcurrent detection input pin, low level overcurrent Overall mode downstream port overcurrent detection input pin, low level overcurrent |

|----|----|----|-----------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27 | -  | -  | OVCUR2#         | 5I | Downstream port 2 overcurrent detection input pin, low level overcurrent                                                                                     |

| 22 | -  | -  | OVCUR3#         | I  | Downstream port 3 overcurrent detection input pin, low level overcurrent                                                                                     |

| 21 | -  | -  | OVCUR4#         | I  | Downstream port 4 overcurrent detection input pin, low level overcurrent                                                                                     |

| 35 | -  | -  | OVCUR5#         | I  | Downstream port 5 overcurrent detection input pin, low level overcurrent                                                                                     |

| 38 | -  | -  | OVCUR6#         | I  | Downstream port 6 overcurrent detection input pin, low level overcurrent                                                                                     |

| 37 | -  | -  | OVCUR7#         | I  | Downstream port 7 overcurrent detection input pin, low level overcurrent                                                                                     |

| -  | -  | 22 | OVCUR#          | 5I | Overall mode downstream port overcurrent detection input pin, low level overcurrent                                                                          |

| -  | 45 | -  | OVCUR123<br>4#  | 5I | Downstream port 1/2/3/4 overcurrent detection input pin, low level overcurrent                                                                               |

| -  | 43 | -  | OVCUR567<br>#   | 5I | Downstream port 5/6/7 overcurrent detection input pin, low level overcurrent                                                                                 |

| 29 | -  | -  | PWREN1          | Ο  | Downstream port 1 power output control pin, high level enabled  Overall mode downstream port power output control pin, high level enabled                    |

| 26 | -  | -  | PWREN2          | О  | Downstream port 2 power output control pin, high level enabled                                                                                               |

| 23 | -  | -  | PWREN3          | О  | Downstream port 3 power output control pin, high level enabled                                                                                               |

| 20 | -  | -  | PWREN4          | О  | Downstream port 4 power output control pin, high level enabled                                                                                               |

| 30 | -  | -  | PWREN5          | О  | Downstream port 5 power output control pin, high level enabled                                                                                               |

| 39 | -  | -  | PWREN6          | О  | Downstream port 6 power output control pin, high level enabled                                                                                               |

| 36 | -  | -  | PWREN7          | О  | Downstream port 7 power output control pin, high level enabled                                                                                               |

| -  | 44 | 21 | PWREN#          | О  | Overall mode downstream port power output control pin, low level enabled                                                                                     |

| 51 | 3  | -  | LED_A1/<br>LED1 | O  | LED_A1: Downstream port 1 normal status indication signal LED1: Downstream port 1 status indication signal                                                   |

| 49 | 4  | _  | LED_A2/         | О  | LED_A2: Downstream port 2 normal status indication                                                                                                           |

|    |       |       | LED2     |                                                                                          | aional                                                     |

|----|-------|-------|----------|------------------------------------------------------------------------------------------|------------------------------------------------------------|

|    |       |       | LED2     |                                                                                          | signal                                                     |

|    |       |       |          |                                                                                          | LED2: Downstream port 2 status indication signal           |

| 47 | _     | _     | LED_A3/  |                                                                                          | LED_A3: Downstream port 3 normal status indication         |

| 47 | 5     | -     | LED2     | О                                                                                        | signal                                                     |

|    |       |       |          |                                                                                          | LED3: Downstream port 3 status indication signal           |

| 22 | 7     |       | LED_A4/  |                                                                                          | LED_A4: Downstream port 4 normal status indication         |

| 33 | 7     | -     | LED4     | О                                                                                        | signal                                                     |

|    |       |       |          |                                                                                          | LED4: Downstream port 4 status indication signal           |

| 21 | 40    |       | LED_A5/  |                                                                                          | LED_A5: Downstream port 5 normal status indication         |

| 31 | 48    | -     | LED5     | О                                                                                        | signal                                                     |

|    |       |       |          |                                                                                          | LED5: Downstream port 5 status indication signal           |

| 17 | 47    |       | LED_A6/  |                                                                                          | LED_A6: Downstream port 6 normal status indication         |

| 17 | 47    | _     | LED6     | О                                                                                        | signal                                                     |

|    |       |       |          |                                                                                          | LED 6: Downstream port 6 status indication signal          |

| 15 | 16    |       | LED_A7/  |                                                                                          | LED_A7: Downstream port 7 normal status indication         |

| 13 | 46    | _     | LED7     | О                                                                                        | signal LED7: Downstream port 7 status indication signal    |

|    |       |       |          |                                                                                          | LED DRV: LED indicator LED drive control signal            |

|    |       |       |          |                                                                                          | SMB EN: It is used as a configuration pin during reset     |

|    | 1     |       | LED_DRV/ | I/O                                                                                      | to configure IIC mode or SMBus mode. Floating or           |

| _  | - 1 - | _     | SMB_EN   | 1/0                                                                                      |                                                            |

|    |       |       |          | high level is IIC mode, low level is SMBus mode, and it has a built-in pull-up resistor. |                                                            |

|    |       |       |          |                                                                                          | LED B1: Downstream port 1 abnormal status                  |

| 50 | -     | -     | LED_B1   | О                                                                                        | indication signal                                          |

|    |       |       |          |                                                                                          | LED B2: Downstream port 2 abnormal status                  |

| 48 | -     | -     | LED_B2   | О                                                                                        | indication signal                                          |

|    |       |       |          |                                                                                          | LED B3: Downstream port 3 abnormal status                  |

|    |       |       |          |                                                                                          | indication signal                                          |

|    |       |       |          |                                                                                          | GANG EN: It is used as a configuration pin during          |

| 34 | _     | _     | LED_B3/  | I/O                                                                                      | reset to configure the overall mode or independent         |

|    |       |       | GANG_EN  |                                                                                          | mode. The floating or high level is independent mode,      |

|    |       |       |          |                                                                                          | and the low level is overall mode. It has a built-in pull- |

|    |       |       |          |                                                                                          | up resistor.                                               |

|    |       |       |          | _                                                                                        | LED B5: Downstream port 5 abnormal status                  |

| 18 | -     | -     | LED_B5   | О                                                                                        | indication signal                                          |

|    |       |       |          |                                                                                          | SUSP: SUSPEND sleep state output pin, high level           |

|    |       |       |          |                                                                                          | indicates sleep state, low level indicates normal state;   |

|    |       | SUSP/ |          | PSELF: It is used as a configuration pin during reset to                                 |                                                            |

| 45 | _     |       |          | I/O                                                                                      | configure the power supply mode. The floating or high      |

|    |       |       | PSELF    |                                                                                          | level is the self-power supply mode, and the low level     |

|    |       |       |          |                                                                                          | is the bus power supply mode. It has a built-in pull-up    |

|    |       |       |          |                                                                                          | resistor.                                                  |

| 13 |       |       | CFG2     | I                                                                                        | CH338X chip function configuration pin 2                   |

| 42 |       |       | HS_S/    | I/O                                                                                      | CH338X chip function configuration pin 1                   |

|            |          |    | CFG1      |            | HS S: Upstream port speed status output pin, high               |

|------------|----------|----|-----------|------------|-----------------------------------------------------------------|

|            |          |    |           |            | level indicates USB high-speed, low level indicates             |

|            |          |    |           |            | USB full-speed;                                                 |

|            |          |    |           |            | It serves as a configuration pin during reset and               |

|            |          |    |           |            | cooperates with CFG2 and CGF0 for functional                    |

|            |          |    |           |            | configuration.                                                  |

| 41         |          |    | CFG0      | I          | CH338X chip function configuration pin 0                        |

| 44         | 41       |    | VDIIC DET | <b>5</b> I | USB bus V <sub>BUS</sub> status detection input, built-in pull- |

| 44         | 41       | -  | VBUS_DET  | 5I         | down resistor                                                   |

|            |          |    | SCL/      |            | SCL: During reset the EEPROM clock signal line                  |

| 41         | 3        | 18 | SMBCLK    | О          | output                                                          |

|            |          |    | SWIDCLK   |            | SMBCLK: SMBus bus clock signal line                             |

|            |          |    | SDA/      |            | SDA: During reset the EEPROM bidirectional data                 |

| 40         | 2        | 17 | SMBDAT    | I/O        | signal line                                                     |

|            |          |    | SWIDDAI   |            | SMBDAT: SMBus bus data signal line                              |

| l <u>.</u> | _        | 25 | CC1       | I/O        | PD protocol communication pin CC1, used to connect              |

|            |          |    | CCI       | 1/0        | the adapter                                                     |

| _          | _        | 26 | CC2       | I/O        | PD protocol communication pin CC2, used to connect              |

|            |          |    | 002       |            | the adapter                                                     |

| _          | _        | 24 | CC3       | I/O        | PD protocol communication pin CC3, used to connect              |

|            |          |    |           |            | cell phones/computers                                           |

| _          | _        | 27 | CC3 CTL   | O          | CC3_CTL: PD protocol communication pin CC3                      |

|            |          |    | 000_012   |            | control pin                                                     |

|            |          |    |           |            | PD protocol communication power control pin                     |

| _          | _        | 23 | PWR_CTL/  | I/O        | CFG: As a configuration pin during reset, different             |

|            |          | _0 | CFG       |            | operating parameters are configured through different           |

| 10 11      |          |    |           |            | resistors.                                                      |

| 10、14、     |          |    |           |            | Empty pins or reserved pins are prohibited from being           |

| 16、19、     | 21、26、28 | -  | NC        |            | connected.                                                      |

| 32         |          |    |           |            |                                                                 |

Note 1: Pin type abbreviation explanation:

*I: 3.3V signal input. O: 3.3V signal output.*

51: Rated 3.3V signal input; Support 5V tolerant voltage.

P: Power or ground.

# 5. Function Description

#### 5.1 Overcurrent Detection and Power Control

#### **5.1.1 Overcurrent Detection**

CH338X supports two overcurrent protection modes: independent overcurrent mode and overall overcurrent mode. CH338L and CH338F support overall overcurrent mode, as shown in Table 5-1.

Table 5-1 Overcurrent protection control instructions

| Chip model | Overcurrent configuration                                   | Overcurrent mode           | Sampling pin for overcurrent detection                              | Reference<br>figure |

|------------|-------------------------------------------------------------|----------------------------|---------------------------------------------------------------------|---------------------|

| CH338X     | EEPROM default allocation/ GANG_EN = high level             | Independent<br>overcurrent | OVCUR1#, OVCUR2#, OVCUR3#,<br>OVCUR4#, OVCUR5#, OVCUR6#,<br>OVCUR7# | Figure 5-1          |

| СПЭЗОХ     | EEPROM non-default<br>configuration/<br>GANG_EN = low level | Overall overcurrent        | OVCUR1#                                                             | Figure 5-2          |

| CH338L     | -                                                           | Overall overcurrent        | OVCUR1234#, OVCUR567#                                               | Figure 5-2          |

| CH338F     | -                                                           | Overall overcurrent        | OVCUR#                                                              | Figure 5-2          |

#### **5.1.2 Power Supply**

CH338X supports two power control modes: independent power control mode and overall power control mode. CH338L and CH338F support overall power control mode, as shown in Table 5-2.

Table 5-2 Power control instructions

|            | Tuble 5.2.1 Ower control instructions |               |                               |                     |  |  |  |  |  |

|------------|---------------------------------------|---------------|-------------------------------|---------------------|--|--|--|--|--|

| Chip model | Power control configuration           | Power control | Overcurrent power control pin | Reference<br>figure |  |  |  |  |  |

|            | EEPROM default                        |               | PWREN1, PWREN2, PWREN3,       |                     |  |  |  |  |  |

|            | allocation /                          | Independent   | PWREN4,                       | Eigene 5 1          |  |  |  |  |  |

|            | GANG_EN = high                        | overcurrent   | PWREN5, PWREN6, PWREN7        | Figure 5-1          |  |  |  |  |  |

| CH338X     | level                                 |               | Note: High level enabled      |                     |  |  |  |  |  |

|            | EEPROM non-default                    | Overall       | PWREN1                        |                     |  |  |  |  |  |

|            | configuration /                       |               |                               | Figure 5-2          |  |  |  |  |  |

|            | GANG_EN = low level                   | overcurrent   | Note: High level enabled      |                     |  |  |  |  |  |

| CH338L/    |                                       | Overall       | PWREN#                        | Eigung 5 2          |  |  |  |  |  |

| CH338F     | -                                     | overcurrent   | Note: High level enabled      | Figure 5-2          |  |  |  |  |  |

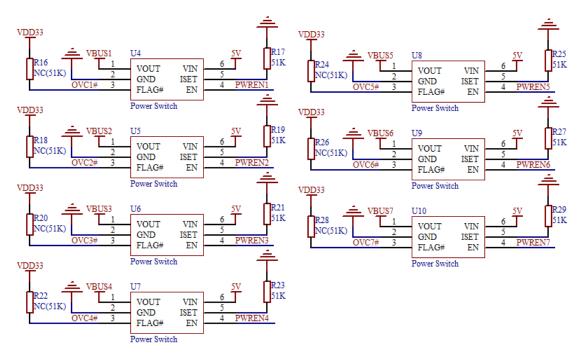

#### 5.1.3 Independent Overcurrent Detection and Independent Power Supply Control

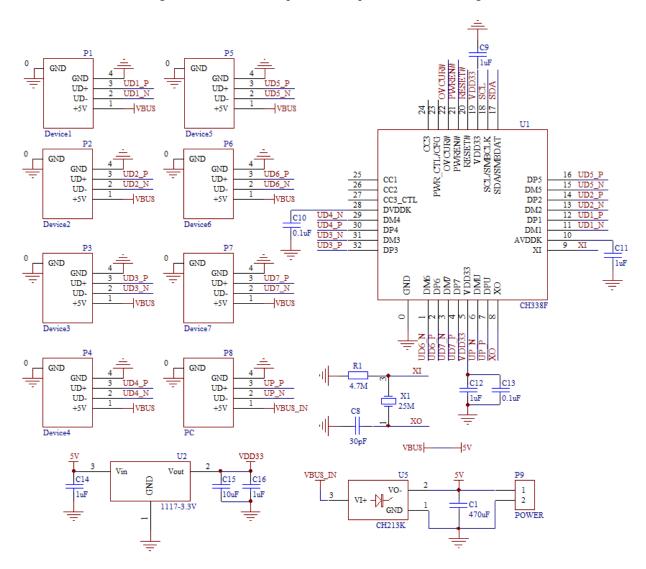

Figure 5-1 CH338X independent overcurrent detection and independent power supply control

In the figure above, V<sub>BUS1</sub>-V<sub>BUS7</sub> are connected to the V<sub>BUS</sub> power pins of downstream ports 1-7 respectively. U4~U10 are USB current-limiting power distribution switch chips with integrated over-current detection for V<sub>BUS</sub> power distribution management. In applications without external power supply of 5V, it is recommended to set the current limit below 1A or even 500mA through ISET external resistor. The FLAG pins of U4~U10 are open-drain outputs and need to be pulled up through resistors respectively. In the default configuration, OC\_LEVEL=0, the OVCUR# pin of the CH338 chip provides a built-in weak pull-up current, so the resistors R16, R18, R20, R22, R24, R26 and R28 can be omitted. If the power switch chip control pin used is active high, the PWREN pin needs to be polarity swapped. The CH338X chip's overcurrent detection pin (OVCURx), downstream port power control pin (PWRENx), and indicator pins (LEDx) all support polarity configuration via configuration pins or EEPROM.

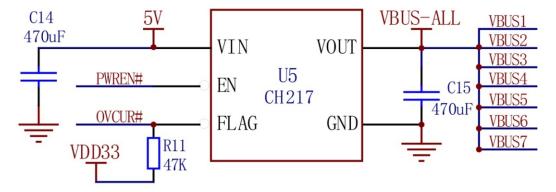

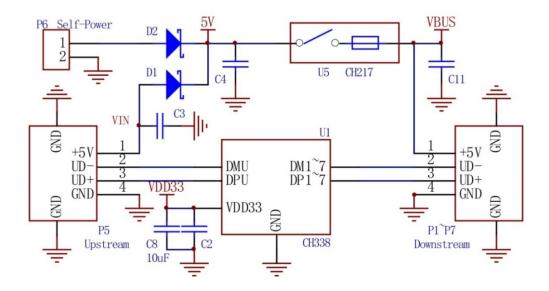

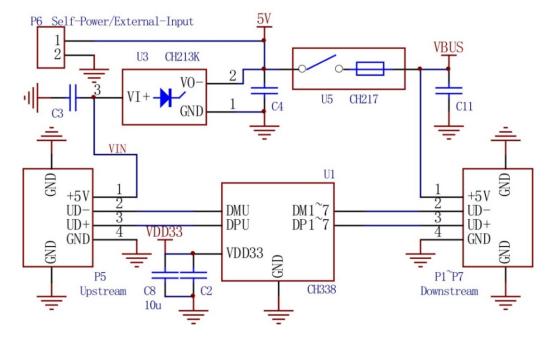

#### 5.1.4 Overall Overcurrent Detection and Overall Power Supply Control

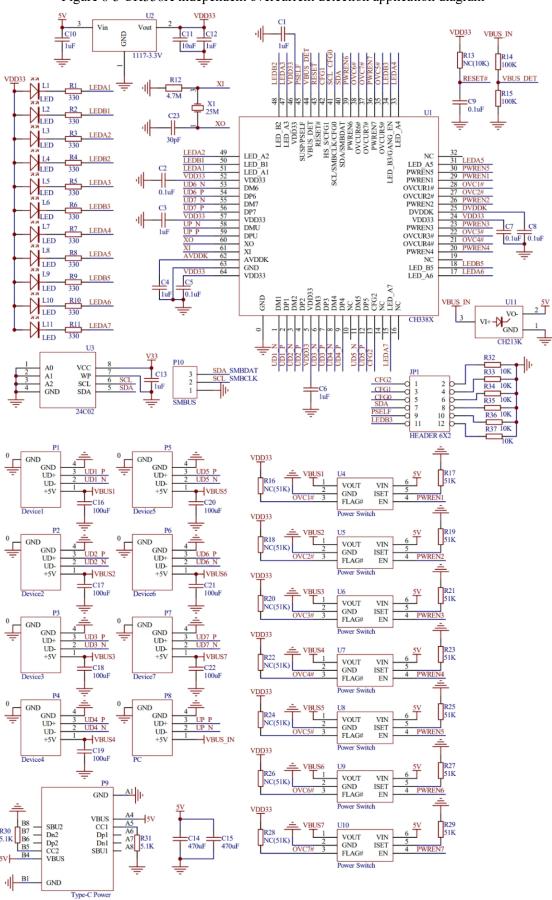

Figure 5-2 Overall overcurrent detection and independent power supply control

U5 is a USB current-limiting power switch chip, such as a CH217 chip or a chip with similar functions. R11 can be omitted in the default configuration. The capacity of C14 can be selected according to needs.  $V_{BUS-ALL}$  is also connected to the  $V_{BUS}$  power pins of downstream ports 1-7. The current limit setting value of U5 needs to consider the 7 downstream ports and whether it is self-powered.

#### 5.2 Reset

There is a power-on reset module embedded in the chip. Under normal circumstances, there is no need to provide an external reset signal. An external reset input pin RESET# is also provided, which has a built-in pull-up resistor.

#### 5.2.1 Power on Reset

When the power supply is powered on, the chip's internal POR power-on reset module will generate a power-on reset sequence and delay Trpor for about 25mS to wait for the power supply to stabilize. During operation, when the power supply voltage is lower than  $V_{lvr}$ , the chip's internal LVR low-voltage reset module will generate a low-voltage reset until the voltage rises, and delays to wait for the power supply to stabilize. Figure 5-3 below shows the power-on reset process and low-voltage reset process.

V<sub>1vr</sub>

VDD33

RESET

DELAY

INTERNAL

RESET

#### 5.2.2 External Reset

The external reset input pin RESET# has a built-in pull-up resistor of about  $40K\Omega$ . If the chip needs to be reset externally, then this pin can be driven low, the internal resistance of the driver is recommended to be no more than  $1K\Omega$ , and the low pulse width of the reset needs to be greater than 4uS.

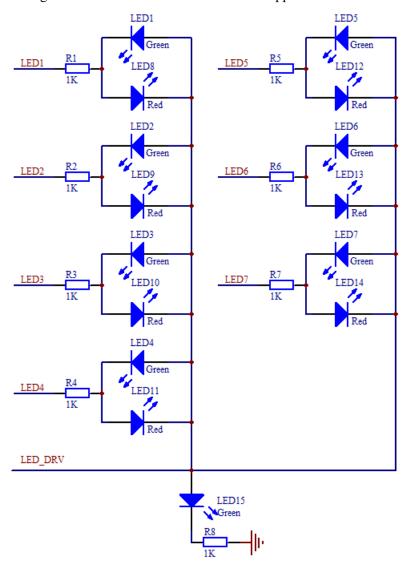

#### **5.3 LED**

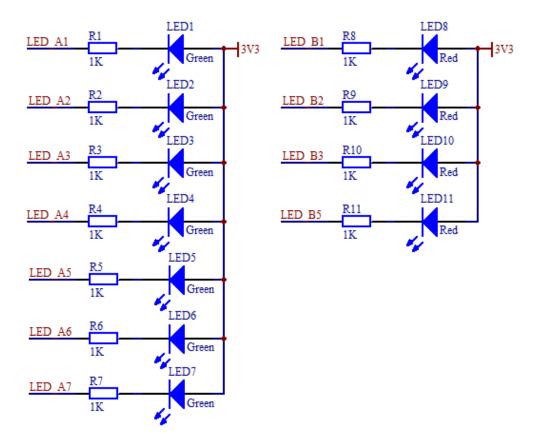

According to the USB2.0 protocol specification, CH338 provides a downstream port status LED indicator control pin, the corresponding green LED of the port is on to indicate the port status is normal, the green LED is off to indicate that there is no device on the port or suspend, and the corresponding red LED of the port is on to indicate that the port is abnormal.

#### 5.3.1 CH338L 15-LED Application

The figure below is a schematic diagram of the complete 15-LED mode application of CH338L, in which LED1-7 are the normal status indicators (Green LED) of ports 1-7 respectively. On indicates that a device is inserted into the port and the port is normal, and off indicates that there is no device on the port or suspend. LED8-14 are the abnormal status indicators (Red LED) of ports 1-7 respectively. When lit, it indicates that the port is abnormal, such as overcurrent. LED15 is the HUB working indicator LED. When it lights up, it indicates that the HUB is normal. When it goes out, it indicates that the HUB is suspended.

Figure 5-4 CH338L overall 15-LED mode application schematic

#### 5.3.2 CH338X 11-LED Application

Figure 5-5 is a schematic diagram of the CH338X 11-LED mode application, in which LED1-7 are the normal status indicators (Green LED) of ports 1-7 respectively. On indicates that a device is inserted into the port and the port is normal, and off indicates that there is no device on the port or suspend. LED8-11 are the abnormal status indicators (Red LED) of ports 1, 2, 3 and 5 respectively. When lit, it indicates that the port is abnormal, such as overcurrent.

Figure 5-5 CH338X 11-LED mode application schematic

# **5.4 I/O Function Configuration**

Some functions of CH338 can be configured in 3 ways: built-in or external EEPROM, SMBus interface and configuration pins. The parameter configuration function of EEPROM has a higher priority than the pin configuration function. Configuration pins are generally multiplexed pins that are used as configuration pins during reset. After the reset is completed, they are switched to the corresponding function pins.

|            | Table 5-3 CH338X main configuration pin descriptions |       |       |                                                          |  |  |  |

|------------|------------------------------------------------------|-------|-------|----------------------------------------------------------|--|--|--|

| Chip model | PIN13                                                | PIN42 | PIN41 | Function description                                     |  |  |  |

| Chip model | CFG2                                                 | CFG1  | CFG0  | i diletion description                                   |  |  |  |

|            |                                                      |       |       | Internal EEPROM configuration parameter function enabled |  |  |  |

|            | 0                                                    | 0     | 0     | Other function configuration pin enabled during reset    |  |  |  |

|            |                                                      |       |       | HUB self-powered mode                                    |  |  |  |

|            |                                                      |       |       | Internal EEPROM configuration parameter function enabled |  |  |  |

|            | 0                                                    | 0     | 1     | SMBus interface enabled                                  |  |  |  |

| CHI220V    | U                                                    | U     |       | Other function configuration pin disabled during reset   |  |  |  |

| CH338X     |                                                      |       |       | HUB self-powered mode                                    |  |  |  |

|            |                                                      |       |       | Internal EEPROM configuration parameter function enabled |  |  |  |

|            | 0                                                    | 1     | 0     | Other function configuration pin enabled during reset    |  |  |  |

|            |                                                      |       |       | USB bus powered mode                                     |  |  |  |

|            | 0                                                    | 1     |       | Internal EEPROM configuration parameter function enabled |  |  |  |

|            | 0                                                    | 1     | 1     | IIC interface enabled                                    |  |  |  |

Table 5-3 CH338X main configuration pin descriptions

|   |   |   | Other function configuration pin disabled during reset   |

|---|---|---|----------------------------------------------------------|

|   |   |   | HUB self-powered mode                                    |

| 1 | 0 | 0 | Internal EEPROM configuration parameter function enabled |

| 1 | 0 | 1 | Other function configuration pin disabled during reset   |

| 1 | 1 | 0 | HUB self-powered mode                                    |

|   |   |   | Internal EEPROM configuration parameter function enabled |

| 1 | 1 | 1 | Other function configuration pin disabled during reset   |

| 1 |   |   | Overall power control, overall overcurrent detection     |

|   |   |   | HUB self-powered mode                                    |

Table 5-4 CH338X auxiliary configuration pin descriptions

| Chip model | Function configuration |          | Pin status and function configuration description               |                 |                                       |  |

|------------|------------------------|----------|-----------------------------------------------------------------|-----------------|---------------------------------------|--|

|            |                        | PIN40    | PIN45                                                           |                 | <b>.</b>                              |  |

|            |                        | SDA/SMBD | AT                                                              | SUSP/PSELF      | Function description                  |  |

|            |                        | 0        |                                                                 | 0               | All ports are removable devices       |  |

|            | Device removal         | 0        |                                                                 | 1               | Port 1 is a non-removable device      |  |

|            | function configuration | 1        |                                                                 | 0               | Port 1/2 is a non-removable device    |  |

|            |                        | 1        |                                                                 | 1               | Ports 1/2/3 is non-removable devices  |  |

|            |                        | PIN34    |                                                                 | Г               | .: 1 : .: .:                          |  |

|            | Current overcurrent,   | GANG_EN  |                                                                 | Fui             | nction description                    |  |

|            | power control mode     | 0        | Overall mode (Overall overcurrent, overall control)             |                 |                                       |  |

| CH338X     | configuration          | 1        | Independent mode (Independent overcurrent, independent control) |                 |                                       |  |

|            |                        | PIN49    | Function description                                            |                 |                                       |  |

|            | Power control pin      | LED_A2   |                                                                 |                 |                                       |  |

|            | polarity configuration | 0        | Active low                                                      |                 |                                       |  |

|            |                        | 1        | Active high                                                     |                 |                                       |  |

|            | Overcurrent detection  | PIN47    |                                                                 | Fu              | nction description                    |  |

|            | pin polarity           | LED_A3   |                                                                 |                 | •                                     |  |

|            | configuration          | 0        |                                                                 | tive high (OC_L | · · · · · · · · · · · · · · · · · · · |  |

|            |                        | 1        | Active low (OC_LEVEL=0)                                         |                 |                                       |  |

|            |                        | PIN33    |                                                                 | Fui             | nction description                    |  |

|            | LED pin polarity       | LED_A4   |                                                                 | ı' 1'1          |                                       |  |

|            | configuration          | 0        |                                                                 | tive high       |                                       |  |

|            |                        | 1        | Ac                                                              | tive low        |                                       |  |

Table 5-5 CH338L auxiliary configuration pin descriptions

| Chip model |               | Pin status and function configuration description |  |  |  |  |  |

|------------|---------------|---------------------------------------------------|--|--|--|--|--|

|            | configuration |                                                   |  |  |  |  |  |

|        |                        | PIN46 | PIN47 |       | Function description                                    |  |  |

|--------|------------------------|-------|-------|-------|---------------------------------------------------------|--|--|

|        | D                      | LED7  | LED6  |       | i unction description                                   |  |  |

|        | Downstream             | 0     | 0     | Downs | Downstream ports 4, 3, 2, 1 enabled                     |  |  |

|        | port enable            | 1     | 0     | Downs | Downstream ports 5, 4, 3, 2, 1 enabled                  |  |  |

|        | configuration          | 0     | 1     | Downs | Downstream ports 6, 5, 4, 3, 2, 1 enabled               |  |  |

|        |                        | 1     | 1     | Downs | Downstream ports 7, 6, 5, 4, 3, 2, 1 enabled            |  |  |

|        |                        | PIN7  | PIN5  | PIN4  | F 1                                                     |  |  |

|        | Device removal         | LED4  | LED3  | LED2  | Function description                                    |  |  |

| CH338L |                        | 1     | 1     | 1     | All ports are removable devices                         |  |  |

|        |                        | 1     | 1     | 0     | Port 2 is a non-removable device                        |  |  |

|        |                        | 1     | 0     | 1     | Ports 3 and 2 are non-removable devices                 |  |  |

|        |                        | 1     | 0     | 0     | Ports 3, 2, and 1 are non-removable devices             |  |  |

|        | function configuration | 0     | 1     | 1     | Ports 4, 3, 2, and 1 are non-removable devices          |  |  |

|        | Configuration          | 0     | 1     | 0     | Ports 5, 4, 3, 2, and 1 are non-removable devices       |  |  |

|        |                        | 0     | 0     | 1     | Ports 6, 5, 4, 3, 2, and 1 are non-removable devices    |  |  |

|        |                        | 0     | 0     | 0     | Ports 7, 6, 5, 4, 3, 2, and 1 are non-removable devices |  |  |

Table 5-6 CH338F configuration pin descriptions

| Chip model | Function configuration                | Pin status an                  | d function configuration description                                      |  |

|------------|---------------------------------------|--------------------------------|---------------------------------------------------------------------------|--|

|            |                                       | PIN23                          | Function description                                                      |  |

|            |                                       | PWR_CTL/CFG                    | i unction description                                                     |  |

|            |                                       | 15KΩ resistance to             | Enable I2C interface, external EEPROM                                     |  |

|            |                                       | ground                         |                                                                           |  |

|            |                                       | 9.1K $\Omega$ resistance to    | Enable SMBus interface                                                    |  |

|            |                                       | ground                         |                                                                           |  |

|            |                                       |                                | Enable the exchange function between the                                  |  |

|            |                                       |                                | upstream port and the downstream PORT1                                    |  |

|            | Device removal function configuration |                                | port, and enable the SMBus interface.                                     |  |

|            |                                       | $3.9$ K $\Omega$ resistance to | Write the register control with the offset address 0xFF through the SMBus |  |

| CH338F     |                                       | ground                         |                                                                           |  |

|            |                                       |                                | interface. Write 0xCO to control                                          |  |

|            |                                       |                                | switching. Writing 0x8O will not switch.                                  |  |

|            |                                       |                                | Writing other values is invalid.                                          |  |

|            |                                       |                                | Enable the exchange function between the                                  |  |

|            |                                       |                                | upstream port and the downstream PORT1                                    |  |

|            |                                       | $2K\Omega$ resistance to       | port, controlled by the SDA pin. There is                                 |  |

|            |                                       | ground                         | no switching when it is left floating or                                  |  |

|            |                                       |                                | pulled up. The input low level controls the                               |  |

|            |                                       |                                | switching.                                                                |  |

|            |                                       | 820Ω resistance to             | Enable 2-wire extension/isolation function                                |  |

|            |                                       | ground                         |                                                                           |  |

### 5.5 EEPROM Configuration Interface

CH338 provides a 2-wire I2C interface to communicate with an external EEPROM memory chip. The EEPROM chip address is 0. The EEPROM stores customized vender ID, product ID, USB string descriptor and functional configuration information. The SCL pin output clock frequency is about 100KHz, and the SDA pin has a built-in pull-up resistor to support open-drain bidirectional data communication without the need for an external pull-up resistor.

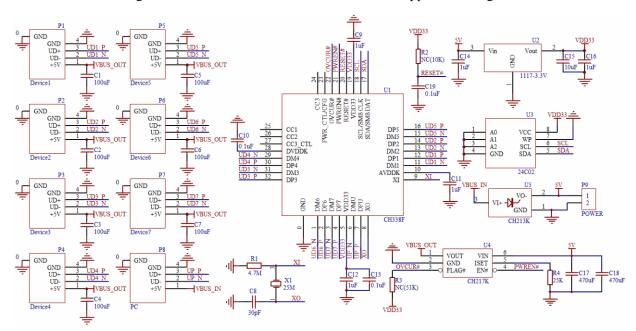

Figure 5-6 External EEPROM connection diagram

CH338 has built-in information memory, which can replace external EEPROM to mass-customize vender or product information and configuration according to the special needs of the industry, such as setting the number of downstream ports, setting the non-removable characteristics of the device of the downstream port, etc.

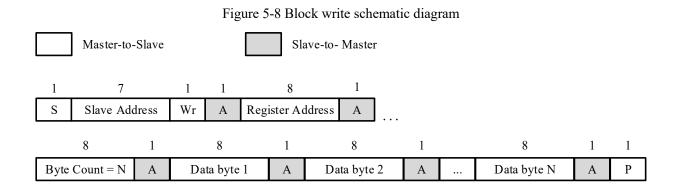

#### **5.6 SMBus Configuration Interface**

CH338 provides a 2-wire SMBus slave interface to communicate with the external master chip. The SMBus interface contains two pins, SMCLK and SMDAT. The communication address is 0x2C. It supports block read and block write operations, and each block is up to 32 bytes. The external master can read and write the EEPROM built into the chip through the SMBus interface. Figure 5-7 is a schematic diagram of block reading, and Figure 5-8 is a schematic diagram of block writing.

Master-to-Slave Slave-to- Master 7 1 8 S S Slave Address Wr A Register Address Slave Address Rd A A 8 1 8 1 1 Byte Count = NData byte 1 A Data byte 2 Data byte N

Figure 5-7 Block read schematic diagram

## 5.7 EEPROM Configuration

CH338 supports loading configuration information such as vender identification code VID, product identification code PID, USB string descriptor and function configuration from external or internal EEPROM. If the information in the EEPROM is invalid, the default configuration information will be automatically loaded. Table 5-7 describes the specific configuration information of EEPROM.

Table 5-7 Internal/External EEPROM configuration information

| Offset address | Parameter abbreviation | Parameter description                                                                                                                                                                                                                                                                                                                                                                                                          | Default value |

|----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 00h            | VID_L                  | The low byte of the vender identification code VID                                                                                                                                                                                                                                                                                                                                                                             | 86h           |

| 01h            | VID_H                  | The high byte of the vender identification code VID                                                                                                                                                                                                                                                                                                                                                                            | 1Ah           |

| 02h            | PID_L                  | The low byte of the product identification code PID CH338 series are 9Eh, CH339 series are 9Fh                                                                                                                                                                                                                                                                                                                                 | 9Eh or 9Fh    |

| 03h            | PID_H                  | The high byte of the product identification code PID                                                                                                                                                                                                                                                                                                                                                                           | 80h           |

| 04h            | bcdDevice_L            | bcdDevice low byte, used for indicating chip package<br>model<br>Fixed, cannot modified                                                                                                                                                                                                                                                                                                                                        | Follow model  |

| 05h            | bcdDevice_H            | bcdDevice high byte, used for indicating chip version Fixed, cannot modified                                                                                                                                                                                                                                                                                                                                                   | Follow model  |

| 06h            | Fun_Cfg1               | Functional configuration byte 1 Bit7: Power supply mode selection;  0: Bus powered mode (Default);  1: Self-powered mode; Bit6: Reserved; Bit5: High-speed mode prohibition control;  0: High-speed mode enabled (Default);  1: High speed mode disabled; Bit4: STT and MTT mode selection;  0: STT mode;  1: MTT mode (Default); Bit3: Reserved; Bit2-1: Port overcurrent function control;  00: Overall overcurrent control; | Follow model  |

|       | 1                 |                                                     |       |

|-------|-------------------|-----------------------------------------------------|-------|

|       |                   | 01: Independent overcurrent control;                |       |

|       |                   | 1x: Does not support overcurrent control;           |       |

|       |                   | Bit0: Port power control;                           |       |

|       |                   | 0: Overall power control;                           |       |

|       |                   | 1: Independent power control;                       |       |

|       |                   | Functional configuration byte 2                     |       |

|       |                   | Bit7: Reserved;                                     |       |

|       |                   | Bit6: Reserved;                                     |       |

|       |                   | Bit5: Reserved;                                     |       |

| 07h   | Fun_Cfg2          | Bit4: Reserved;                                     | 20h   |

|       |                   | Bit3: Whether HUB is Compound Device;               |       |

|       |                   | 0: No;                                              |       |

|       |                   | 1: Yes;                                             |       |

|       |                   | Bit2-0: Reserved;                                   |       |

|       |                   | Functional configuration byte 3                     |       |

|       |                   | Bit7-4: Reserved;                                   |       |

|       |                   | Bit3: Port remapping function control;              |       |

|       |                   | 0: Disabled (Default);                              |       |

| 08h   | Fun Cfg3          | 1: Enabled;                                         | 00h   |

|       | _ 5               | Bit2-1: Reserved;                                   |       |

|       |                   | Bit0: String descriptor enable control;             |       |

|       |                   | 0: Disabled (Default);                              |       |

|       |                   | 1: Enabled;                                         |       |

|       |                   | Whether the downstream port device can be removed   |       |

|       |                   | is controlled                                       |       |

|       |                   | Bit7-1: Is the device on downstream port 7-1        |       |

| 09h   | Dev_<br>Removable | removable?                                          | 00h   |

| 0,511 |                   | 0: Removable (Default);                             | 0 011 |

|       |                   | 1: Not removable;                                   |       |

|       |                   | Bit0: Reserved, must be 0;                          |       |

|       |                   | Port disabled in self-powered mode                  |       |

|       |                   | Bit7-1: Is downstream port 7-1 prohibited?          |       |

| 0Ah   | Port Dis Sp       | 0: Disabled (Default);                              | 00h   |

| 07111 | Tort_Dis_Sp       | 1: Enabled;                                         | 0011  |

|       |                   | Bit0: Reserved, must be 0;                          |       |

|       |                   | Port disabled in bus powered mode                   |       |

|       |                   | Bit7-1: Is downstream port 7-1 prohibited?          |       |

| 0Bh   | Port Die De       | 0: Disabled (Default);                              | 00h   |

| VBII  | Port_Dis_Bp       | 1: Enabled;                                         | OON   |

|       |                   | ·                                                   |       |

|       |                   | Bit0: Reserved, must be 0;                          |       |

| 0Ch   | MaxPwr_Sp         | Maximum operating current in self-power mode, unit  | 01h   |

|       | _ 1               | is 2mA                                              |       |

| 0Dh   | MaxPwr Bp         | Maximum operating current in bus power supply mode, | 64h   |

|       | _ r               | unit is 2mA                                         | -     |

| 0Eh     | HubCurrent_Sp           | Maximum current required by HUB in self-power mode                                                                                                                                                                                                                                                                                 | 01h          |

|---------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 0Fh     | HubCurrent Bp           | Maximum current required by HUB in bus power mode                                                                                                                                                                                                                                                                                  | 64h          |

| 10h     | Pwr_OnTime              | Delay time from when the downstream port is powered on to when the power supply becomes valid                                                                                                                                                                                                                                      | 32h          |

| 11h     | LanguageID_H            | Language ID high byte                                                                                                                                                                                                                                                                                                              | 00h          |

| 12h     | LanguageID_L            | Language ID low byte                                                                                                                                                                                                                                                                                                               | 00h          |

| 13h     | Vendor_StrLen           | Vendor string descriptor length                                                                                                                                                                                                                                                                                                    | 00h          |

| 14h     | Product_StrLen          | Product string descriptor length                                                                                                                                                                                                                                                                                                   | 00h          |

| 15h     | SN_StrLen               | Serial number string descriptor length                                                                                                                                                                                                                                                                                             | 00h          |

| 16h-53h | Vendor String           | Vendor string descriptor  Vendor string descriptor in Unicode format                                                                                                                                                                                                                                                               | 00h          |

| 54h-91h | Product String          | Product string descriptor Product string descriptor in Unicode format                                                                                                                                                                                                                                                              | 00h          |

| 92h-CFh | Serial Number<br>String | Serial number string descriptor Serial number string descriptor in Unicode format                                                                                                                                                                                                                                                  | 00h          |

| D0h     | PortNum                 | Number of downstream ports, valid range: 1-7                                                                                                                                                                                                                                                                                       | Follow model |

| D1h     | bcdUSB_L                | USB version low byte bcdUSB_L=0x00, USB2.00 bcdUSB_L=0x01, USB2.01 bcdUSB_L=0x10, USB2.10                                                                                                                                                                                                                                          | 00h          |

| D2h     | Fun_Cfg4                | Functional configuration byte 4 Bit7-2: Reserved, must be 0; Bit1: Force the downstream port to full-speed mode; 0: High speed mode (Default); 1: Full-speed mode; Bit0: Indicator function enable configuration; 0: Disabled (Default); 1: Enabled;                                                                               | 00h          |

| D3h     | Fun_Cfg5                | Functional configuration byte 5 Bit7: LED indicator polarity configuration; 0: Active low (Default); 1: Active high; Bit6: Port overcurrent detection polarity configuration; 0: Active low (Default); 1: Active high; Bit5: Port power control polarity configuration; 0: Active low (Default); 1: Active high; Bit4-0: Reserved; | 00h          |

| D4-FAh  | Reserved                | Reserved                                                                                                                                                                                                                                                                                                                           | 00h          |

| DT-IAII | 10001 vou               | Downstream port 1-2 remapping configuration                                                                                                                                                                                                                                                                                        | 0011         |

| FBh     | Port_Remap12            | Bit7-4: Physical port 2 remapping 0000: Physical port 2 prohibits remapping;                                                                                                                                                                                                                                                       | 00h          |

|     | <u> </u>     |                                                    |      |

|-----|--------------|----------------------------------------------------|------|

|     |              | 0001: Physical port 2 is mapped to logical port 1; |      |

|     |              | 0010: Physical port 2 is mapped to logical port 2; |      |

|     |              | 0011: Physical port 2 is mapped to logical port 3; |      |

|     |              | 0100: Physical port 2 is mapped to logical port 4; |      |

|     |              | 0101: Physical port 2 is mapped to logical port 5; |      |

|     |              | 0110: Physical port 2 is mapped to logical port 6; |      |

|     |              | 0111: Physical port 2 is mapped to logical port 7; |      |

|     |              | 1000-1111: Invalid;                                |      |

|     |              | Bit3-0: Physical port 1 remapping                  |      |

|     |              | 0000: Physical port 1 prohibits remapping;         |      |

|     |              | 0001: Physical port 1 is mapped to logical port 1; |      |

|     |              | 0010: Physical port 1 is mapped to logical port 2; |      |

|     |              | 0011: Physical port 1 is mapped to logical port 3; |      |

|     |              | 0100: Physical port 1 is mapped to logical port 4; |      |

|     |              | 0101: Physical port 1 is mapped to logical port 5; |      |

|     |              | 0110: Physical port 1 is mapped to logical port 6; |      |

|     |              | 0111: Physical port 1 is mapped to logical port 7; |      |

|     |              | 1000-1111: Invalid;                                |      |

|     |              | Downstream port 3-4 remapping configuration        |      |

|     |              | Bit7-4: Physical port 4 remapping                  |      |

|     |              | 0000: Physical port 4 prohibits remapping;         |      |

|     |              | 0001: Physical port 4 is mapped to logical port 1; |      |

|     |              | 0010: Physical port 4 is mapped to logical port 2; |      |

|     |              | 0011: Physical port 4 is mapped to logical port 3; |      |

|     |              | 0100: Physical port 4 is mapped to logical port 4; |      |

|     |              | 0101: Physical port 4 is mapped to logical port 5; |      |

| l   |              | 0110: Physical port 4 is mapped to logical port 6; |      |

|     |              | 0111: Physical port 4 is mapped to logical port 7; |      |

| FCh | Port_Remap34 | 1000-1111: Invalid;                                | 00h  |

|     |              | Bit3-0: Physical port 3 remapping                  |      |

|     |              | 0000: Physical port 3 prohibits remapping;         |      |

|     |              | 0001: Physical port 3 is mapped to logical port 1; |      |

|     |              | 0010: Physical port 3 is mapped to logical port 2; |      |

|     |              | 0011: Physical port 3 is mapped to logical port 3; |      |

|     |              | 0100: Physical port 3 is mapped to logical port 4; |      |

|     |              | 0101: Physical port 3 is mapped to logical port 5; |      |

|     |              | 0110: Physical port 3 is mapped to logical port 6; |      |

|     |              | 0111: Physical port 3 is mapped to logical port 7; |      |

|     |              | 1000-1111: Invalid;                                |      |

|     |              | Downstream port 5-6 remapping configuration        |      |

|     | Port_Remap56 | Bit7-4: Physical port 6 remapping                  | 0.53 |

| FDh |              | 0000: Physical port 6 prohibits remapping;         | 00h  |

|     |              | 0001: Physical port 6 is mapped to logical port 1; |      |

|     |              | 0010: Physical port 6 is mapped to logical port 2; |      |

|     | 1           |                                                                                                                                                                |     |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |             | 0011: Physical port 6 is mapped to logical port 3;<br>0100: Physical port 6 is mapped to logical port 4;<br>0101: Physical port 6 is mapped to logical port 5; |     |

|     |             | 0110: Physical port 6 is mapped to logical port 6;                                                                                                             |     |