# High-speed USB Signal Isolation Extender Control Chip CH318

Datasheet Version: V1.1 https://wch-ic.com

# 1. Overview

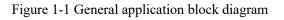

CH318 is a high-speed USB signal isolation and transmission distance extension control chip that supports capacitive coupling or network transformer coupling. It not only realizes the isolation of USB signals, but also realizes real-time relay and transmission distance extension of USB signals. In addition, the CH318 chip itself has a USBHUB function. The upstream port supports USB2.0 high-speed, and the downstream port supports USB2.0 high-speed 480Mbps, full-speed 12Mbps and low-speed 1.5Mbps. CH318 can be used for high-speed USB signal isolation, HUB extension, etc.

The figure below is its general application block diagram.

# 2. Features

- The host computer mode provides 1 USB2.0 downstream port, the slave computer mode provides 2 USB2.0 downstream ports, and is backward compatible with the USB1.1 protocol specification.

- Support 480Mbps high-speed, 12Mbps full-speed and 1.5Mbps low-speed USB transfer

- Support USB control transmission, batch transmission, interrupt transmission, synchronous/isochronous transmission

- The same chip can be configured in host computer mode and slave computer mode to connect USB-Host host and USB-Device device respectively.

- With CH339 chip, it can realize the isolation of USB card reader, USB to SPI, to JTAG, to I2C and other interfaces.

- Support connection status indication

- Built-in capacitive coupling drive circuit and network transformer coupling drive circuit

- A pure hardware solution that is completely real-time and transparent to the USB protocol. It does not require the installation of any additional drivers and supports various systems that include USB interfaces.

- Provide crystal oscillator, supports external clock input, built-in PLL provides 480MHz clock for USBPHY

- The upstream port has a built-in  $1.5K\Omega$  pull-up resistor, and the downstream port has a built-in pull-down

resistor required by the USB Host, simplifying the peripherals.

- USB interface pins with 6kV enhanced ESD performance, Class 3A

- Industrial-grade temperature range: -40 ~ 85°C

- Available in TSSOP20 package

# 3. Package

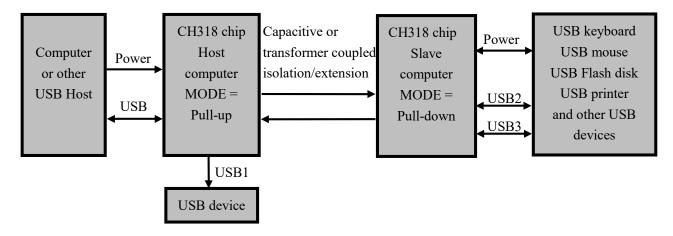

Figure 3-1 Package description

| Package form | Shaping width | Pin spacing |         | Package description               | Order model |

|--------------|---------------|-------------|---------|-----------------------------------|-------------|

| TSSOP20      | 4.4*6.5mm     | 0.65mm      | 25.6mil | Thin Shrink Small Outline Package | CH318T      |

## 4. Pins

| Pin No. | Pin name          | Type <sup>(1)</sup> | Function description                                                  |  |  |

|---------|-------------------|---------------------|-----------------------------------------------------------------------|--|--|

| 1       | DMX               | Analog signal       | Connect directly to the negative end of the differential extension    |  |  |

|         |                   |                     | line through an isolation capacitor or transformer.                   |  |  |

| 2       | DDV               | Analog signal       | Connect directly to the positive end of the differential extension    |  |  |

| 2       | DPX               |                     | cable through an isolation capacitor or transformer.                  |  |  |

| (       |                   | USB                 | Host computer mode: Upstream port USB2.0 signal line D-;              |  |  |

| 6       | DMU               |                     | Slave computer mode: 1# downstream port USB2.0 signal line D-         |  |  |

| 7       | DPU               | USB                 | Host computer mode: Upstream port USB2.0 signal line D+;              |  |  |

| /       |                   |                     | Slave computer mode: 1# downstream port USB2.0 signal line D+         |  |  |

| 8       | DM2               | USB                 | 2# downstream port USB signal line D-                                 |  |  |

| 9       | DP2               | USB                 | 2# downstream port USB signal line D+                                 |  |  |

| 3       | ХО                | 0                   | The inverting output terminal of the crystal oscillator, connected to |  |  |

| 3       |                   |                     | the other terminal of the external crystal.                           |  |  |

| 4       | XI                | Ι                   | Crystal oscillator input terminal, connected to one terminal of the   |  |  |

| 4       |                   |                     | external crystal                                                      |  |  |

| 16      | V <sub>DD33</sub> | Р                   | Analog power input, external 3.3V, external 1uF decoupling            |  |  |

|         |                   |                     | capacitor                                                             |  |  |

Figure 4-1 Pin definition

| 5                 | AV <sub>DDK</sub> | Р    | Analog core power supply, external 1uF decoupling capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14                | DV <sub>DDK</sub> | Р    | Digital core power supply, external 0.1uF decoupling capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15                | GND               | Р    | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13                | LED/MO<br>DE      | 51/O | LED: Host computer and slave computer chip connection status<br>output, active low, built-in pull-up resistor.<br>MODE: During reset, it is used as the host computer or slave<br>computer mode configuration pin. If it is left floating or pulled up<br>through a resistor, it is in host computer mode. If it is pulled down<br>through a 5.1K resistor, it is in slave computer mode.                                                                                                     |

| 10                | IO1               | 51/O | Downstream general-purpose I/O sideband signals have tens of milliseconds of delay in pin mapping. It is an input pin in host computer mode; it is an output pin in slave computer mode. If the IO1 pin in the host computer mode inputs a high level, the corresponding IO1 pin in the slave computer mode outputs a high level; if the IO1 pin in the host computer mode inputs a low level, the corresponding IO1 pin in the slave computer mode outputs low level.                        |

| 11                | IO2               | 51/O | The upstream general-purpose I/O sideband signal has a delay of<br>tens of milliseconds in pin mapping.<br>It is an output pin in host computer mode; it is an input pin in slave<br>computer mode. If the IO2 pin in the slave computer mode inputs<br>a high level, the corresponding IO2 pin in the host computer mode<br>outputs a high level; if the IO2 pin in the slave computer mode<br>inputs a low level, the IO2 pin corresponding to the host computer<br>mode outputs low level. |

| 12                | IO3               | 51/O | The upstream general-purpose I/O sideband signal has a delay of<br>tens of milliseconds in pin mapping. It is an output pin in host<br>computer mode; it is an input pin in slave computer mode. If the<br>IO3 pin in slave computer mode inputs a high level, the<br>corresponding IO3 pin in the host computer mode outputs a high<br>level; if the IO3 pin in the slave computer mode inputs a low level,<br>the corresponding IO3 pin in the host computer mode outputs low<br>level      |

| 17, 18, 19,<br>20 | NC                | -    | Pins are reserved, connections are prohibited                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Note 1: Pin type abbreviations:

USB = USB signal input;

I = 3.3V signal input;

O = 3.3V signal output;

5*I* = *Rated* 3.3*V* signal input, support 5*V* tolerant voltage;

P = Power or ground.

# 5. Function Description

### 5.1 Mode Configuration

The CH318 chip can be configured to connect to USB-Host host and USB-Device devices respectively by configuring pin LED/MODE for host and slave modes.

| Configure pin<br>LED/MODE          | Mode description                                                               |  |  |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| Pull down to GND via 5.1K resistor | Slave computer mode, the downstream port is connected to the USB-Device device |  |  |  |  |  |

|                                    | Host computer mode, the upstream port is connected to the USB-Host host        |  |  |  |  |  |

## 5.2 General Function Description

When the CH318 chip works in the host computer mode, it is recognized as a standard USBHUB on the computer. In addition to the isolation extension interface connected to the host computer chip, it also provides a USB2.0 downstream port for connecting USB keyboard, USB mouse, USB devices such as disks and printers. When working in slave computer mode, it provides 2 USB2.0 downstream ports for connecting USB keyboards, USB mice, U disks, printers and other general USB devices.

CH318 chip supports connection status indication, which is active at low level. If the connection is successful, the LED pin will output low level, and if the connection is disconnected, the LED pin will output high level.

The CH318 chip can use Category 5 or Category 5e UTP (network cables) or USB signal lines and similar differential signal twisted pairs. If the characteristic impedance of the signal lines does not match, the output pins need to be connected in series or parallel resistance.

CH318 chip can use two high-frequency capacitors with a capacity of 0.022uF to 0.47uF to transmit signals and isolate DC voltages in a differential manner. The isolation voltage is determined by the capacitor's withstand voltage, and it is recommended to select a high voltage high-frequency capacitor with a withstand voltage of not less than 2KV of 0.1uF.

CH318 chip can use a network transformer to differentially transmit signals and isolate DC voltage. The isolation voltage is determined by the withstand voltage of the transformer. It is recommended to choose a network transformer with a withstand voltage of not less than 2KV and a rate of not less than 500Mbps. In applications that only isolate but do not extend, the high-frequency parameter requirements of the network transformer can be reduced. The anti-interference effect and voltage resistance performance of transformer coupling are better than capacitive coupling.

CH318 is a pure hardware solution for USB signal line electrical isolation and USB signal extension. It complies with relevant technical specifications and is completely transparent to the USB protocol. The CH318 chip itself does not require any additional driver installation, but the USB device itself may need to install a driver. The method is the same as before it was not extended or isolated. Ordinary USB devices such as U disks, keyboards, and mice do not require drivers.

CH318 chip can automatically identify USB high-speed, USB full-speed and USB low-speed devices, supports plug-and-play, and can automatically detect the connection and disconnection of USB devices. The CH318 chip can be used to make USB signal isolators to reduce signal interference and improve signal collection accuracy; it can also be used to make USB extension cables to extend the USB transmission distance to 20 meters to achieve remote signal collection and online control; it can also be used with the CH339 chip cooperates to realize the isolation of

USB card reader, USB to SPI isolation, USB to JTAG isolation, etc.

## 6. Parameters

**6.1 Absolute Maximum Value** (Critical or exceeding the absolute maximum value will probably cause the chip to work improperly or even be damaged)

| Name              | Parameter Description                                                                                             | Min. | Max.                   | Unit |

|-------------------|-------------------------------------------------------------------------------------------------------------------|------|------------------------|------|

| TA                | Ambient temperature during operation                                                                              | -40  | 85                     | °C   |

| TJ                | Junction temperature range                                                                                        | -40  | 100                    | °C   |

| Ts                | Ambient temperature during storage                                                                                | -55  | 150                    | °C   |

| V <sub>DD33</sub> | Working power supply voltage (V <sub>DD33</sub> pin is connected to power supply, GND pin is connected to ground) | -0.4 | 4.0                    | V    |

| V <sub>USB</sub>  | Voltage on USB signal pin                                                                                         | -0.4 | V <sub>DD33</sub> +0.4 | V    |

| V <sub>GPIO</sub> | The voltage on other (3.3V) input or output pins                                                                  | -0.4 | V <sub>DD33</sub> +0.4 | V    |

| VESDUSB           | HBM ESD tolerant voltage on USB signal pins                                                                       | 6K   |                        | V    |

| VESDIO            | HBM ESD tolerant voltage on other pins                                                                            | 2    | V                      |      |

### 6.2 Electrical Parameters (Test conditions: T<sub>A</sub>=25°C, V<sub>DD33</sub>=3.3V)

| Name              | Parameter Description                           |                         |                            | Min.                   | Тур.                   | Max.              | Unit |

|-------------------|-------------------------------------------------|-------------------------|----------------------------|------------------------|------------------------|-------------------|------|

| V <sub>DD33</sub> | External supply 3.3V voltage @V <sub>DD33</sub> |                         |                            | 3.2                    | 3.3                    | 3.4               | V    |

|                   |                                                 | Upstream high-<br>speed | 2 downstream<br>high-speed |                        | 80                     |                   | mA   |

| I <sub>CC</sub>   | Working current                                 | Upstream high-<br>speed | 1 downstream<br>high-speed |                        | 68                     |                   | mA   |

|                   |                                                 | Upstream high-<br>speed | 2 downstream<br>full-speed |                        | 55                     |                   | mA   |

| V <sub>IL</sub>   | Low level input voltage                         |                         |                            | 0                      |                        | 0.8               | V    |

| V <sub>IH</sub>   | High level input voltage                        |                         |                            | 2.0                    |                        | V <sub>DD33</sub> | V    |

| Vol               | Low level output voltage                        |                         | Sink current<br>5mA        |                        | 0.4                    | 0.6               | V    |

| V <sub>OH</sub>   | High level                                      | output voltage          | Source current<br>5mA      | V <sub>DD33</sub> -0.6 | V <sub>DD33</sub> -0.4 |                   | V    |

| R <sub>PU</sub>   | Pull-up equivalent resistance                   |                         | 30                         | 40                     | 55                     | kΩ                |      |

| R <sub>PD</sub>   | Pull-down equivalent resistance                 |                         | 30                         | 40                     | 55                     | kΩ                |      |

| Vlvr              | Voltage threshold for power low voltage reset   |                         |                            | 2.4                    | 2.9                    | 3.2               | V    |

# 7. Package

Note: All dimensions are in mm (millimeters).

The pin center spacing values are nominal values, with no error. Other than that, the dimensional error is not greater than the greater of  $\pm 0.2$ mm.

# 7.1 TSSOP20

# 8. Application

#### 8.1 Network Transformer Isolated USB Extender

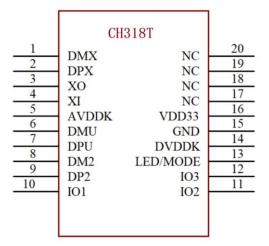

Figure 8-1 CH318T transformer isolation/extension application reference circuit diagram

The figure above is a USB extender that uses network transformer coupling and isolation. The upper part is the host computer module and the lower part is the slave computer module. The two are connected through a network cable. When JP1 is left unconnected, CH318T works in host computer mode. P2 serves as the upstream port of the HUB

and is connected to a computer or other USB-Host. P1 serves as the downstream port of the HUB and connects to USB keyboards, USB mice, U disks, printers and other general USB devices; JP1 If short-circuited, CH318T works in slave computer mode, and P1 and P2 are used as HUB downstream ports. U2 is a 5V to 3.3V linear regulator chip (LDO). Try to choose a model with wide input range and low voltage drop. It is recommended to have a load capacity of no less than 500mA and a heat dissipation mechanism to ensure that the output can be stable at 3.3V.

U3\_1 is the network transformer at the host computer module end, and U3\_2 is the network transformer at the slave computer module end. If the extension distance is short or the same board is used for isolation, one network transformer can be omitted. P3\_1 and P3\_2 are RJ45 interfaces used to connect the host computer module and the slave computer module.

The host computer module and the slave computer module are usually connected using ordinary network cables (Category 5 or Category 5e UTP). For applications that require isolation, the connecting cable only includes two differential signal lines, DPX and DMX, excluding Power and ground wires. For applications that do not require isolation but only extension, two ordinary 8-core network cables can be used for differential signal lines, 4 for ground wires, and 2 for power wires. The power cord can be used to provide +5V power to the USB device side at the same time, but due to the voltage drop of the DC resistance of the network cable, especially when the USB device consumes a lot of current, the actual power supply voltage at the USB device side is usually less than 5V, and even in some cases The USB device may not work properly because of this, so it is necessary to provide independent power supply to the slave computer.

At the moment when the USB device on the HUB downstream port is hot-plugged, the dynamic load may cause the 5V voltage to drop instantaneously, which may cause an LVR low-voltage reset, causing the entire HUB to be disconnected and reconnected. Improvement method: ① Increase the electrolytic capacitor of the 5V power supply within the scope allowed by the specification (Increase the capacity of C10 in the picture) to alleviate the drop; ② Increase the capacitance of the HUB chip power input end (Increase the capacity of C2 or C7 in the picture, for example 22uF) ;③ Enhance 5V power supply capability or change to self-power supply. In addition, improving the quality of USB cable will also improve power supply capability.

When designing the PCB, you need to consider the actual operating current carrying capacity. The PCB of the 5V and P2 and GND trace paths of each port should be as wide as possible. If there are vias, it is recommended to connect multiple ones in parallel. The D+ and D- signal lines of the USB port are wired in parallel according to the high-speed USB specification to ensure characteristic impedance. Try to provide ground wires or copper coating on both sides to reduce signal interference from the outside world.

5V overvoltage protection is recommended, and ESD protection is recommended for all USB signals, e.g. CH412K, whose VCC should be connected to 3.3V.

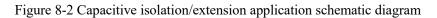

#### 8.2 Capacitive Isolated USB Extender

CH318 chip can use two high-frequency capacitors with a capacity of 0.022uF to 0.47uF to transmit signals and isolate DC voltages in a differential manner. The isolation voltage is determined by the capacitor's withstand voltage, and it is recommended to select a high voltage high-frequency capacitor with a withstand voltage of not less than 2KV of 0.1uF.

When using the capacitor solution for isolation, you only need to replace the transformer in Figure 8-1 with two pairs of high-frequency capacitors, and the other parts remain unchanged. If it is just isolation and no extension is needed, you can omit a pair of capacitors.

#### 8.3 More USB Ports or Other Interface Isolation Extensions

If some applications need to isolate or extend more USB ports, such as 7 USB ports, the slave computer module chip can be replaced with a CH338F chip that turns on the 2-wire extended isolation function. This chip has 7 downstream USB ports.

If some applications need to isolate or extend more USB ports as well as other interfaces, such as network ports, SDIO card reader interfaces, SPI interfaces, JTAG interfaces, UART interfaces, I2C interfaces, etc., the slave computer module chip can be replaced with the CH339W chip that opens the 2-wire extension isolation function, which integrates the functions of a 7-port USB HUB, a USB 100 Gigabit Ethernet, a USB high-speed SD card reader, and a USB-to-SPI, USB-to-JTAG, USB-to-UART, and USB-to-I2C interface.