# Ethernet Protocol Stack Chip CH394

Version: 1.0 https://wch-ic.com

## 1. Overview

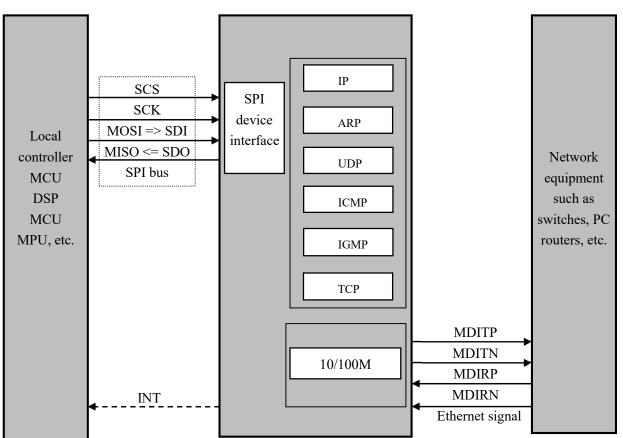

CH394 is an Ethernet protocol stack management chip, which is used for Ethernet communication in MCU system. CH394 chip comes with 10/100M Ethernet Media Access Control (MAC) and Physical layer (PHY), which is fully compatible with IEEE802.3 protocol, and has built-in Ethernet protocol stack firmware such as IP, ARP, ICMP, IGMP, UDP and TCP. MCU system can conveniently communicate with the network through CH394 chip. CH394 supports Wake-on-LAN (WOL) and power-down mode.

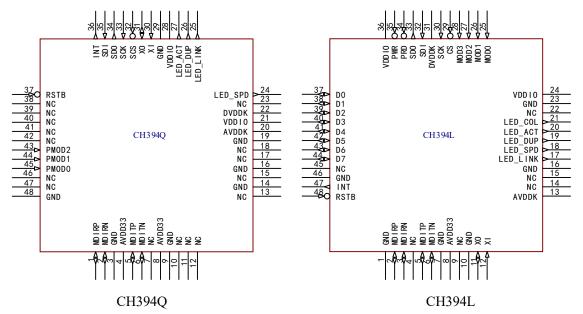

CH394Q provides SPI interface, CH394L provides SPI interface and 8-bit slave parallel interface. Controllers such as MCU/DSP/MCU/MPU can control CH394Q chip to communicate with Ethernet through SPI interface. Or through SPI interface or 8-bit parallel port to control CH394L chip for Ethernet communication.

The contents of this manual are mainly applicable to CH394Q and CH394L. For details, please refer to the CH394DS2 manual.

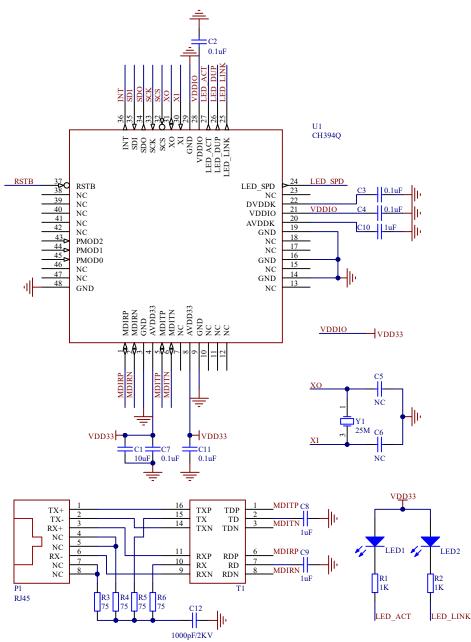

The following figure shows the application block diagram of CH394Q.

Figure 1-1 CH394Q application block diagram

## 2. Features

- Built-in Ethernet Media Access Control (MAC) and Physical layer (PHY)

- Support 10/100M, full-duplex/half-duplex adaptation, and is compatible with 802.3 protocol

- Support automatic conversion of MDI/MDIX lines

- Built-in TCP/IP protocol suite. Support IPv4, ARP, ICMP, IGMP, UDP and TCP protocols

- CH394Q supports 8 sockets and CH394L supports 4 sockets. Can transmit and receive data at the same time

- Support MAC RAW mode and IP RAW mode (IP RAW mode is only supported by CH394L)

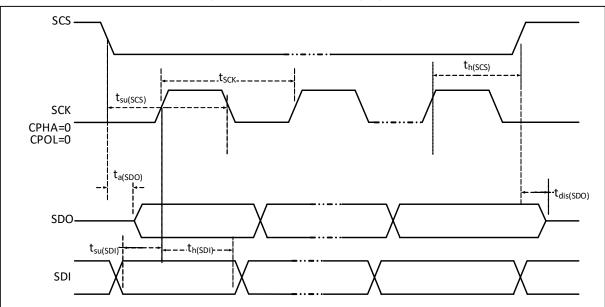

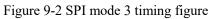

- Provide a SPI slave interface (SPI mode 0 or 3) up to 40MHz, with the high bit coming first

- The CH394L provides a high-speed 8-bit slave parallel interface that supports a parallel data bus connected to the microcontroller.

- Support network Wake-on-LAN (WOL) and power-down mode

- LED status display (Link, ACT, 10/100M, full-duplex/half-duplex, etc.)

- Built-in 32KRAM can be used for Ethernet data transceiver, and each Socket transceiver buffer can be configured flexibly

- LQFP48 lead-free package is provided.

## 3. Package

Table 3-1 Package description

| Package form | Body size | Pin pitch |         | Package description        | Order model |

|--------------|-----------|-----------|---------|----------------------------|-------------|

| LQFP48       | 7*7mm     | 0.5mm     | 19.7mil | Low Profile Quad Flat Pack | CH394Q      |

| LQFP48       | 7*7mm     | 0.5mm     | 19.7mil | Low Profile Quad Flat Pack | CH394L      |

## 4. CH394Q Pins

| CH394Q                                                     | Pin name     |       | Din description                                                                                                                                                                           |  |

|------------------------------------------------------------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No.                                                    | Pin name     | Туре  | Pin description                                                                                                                                                                           |  |

| 1                                                          | MDIRP        | I/O   | Differential input in 10BASE-T/100BASE-TX MDI mode;                                                                                                                                       |  |

| 2                                                          | MDIRN        | 1/0   | Differential output in 10BASE-T/100BASE-TX MDIX mode.                                                                                                                                     |  |

| 5                                                          | MDITP        | I/O   | Differential output in 10BASE-T/100BASE-TX MDI mode;                                                                                                                                      |  |

| 6                                                          | MDITN        | 10    | Differential input in 10BASE-T/100BASE-TX MDIX mode.                                                                                                                                      |  |

| 4                                                          | AVDD33       | Р     | For 3.3V main power input, it is recommended to place $0.1 \text{uF}$ in parallel with 10uF or 4.7uF ground capacitance close to the chip, or a single $1 \text{uF} \sim 4.7 \text{uF}$ . |  |

| 8                                                          | AVDD33       | Р     | 3.3V power input, it is recommended to connect 0.1uF or 1uF capacitor to ground.                                                                                                          |  |

| 20                                                         | AVDDK        | Р     | The external 1uF capacitor to ground is placed close to the chip.                                                                                                                         |  |

| 21、28                                                      | VDDIO        | Р     | For the power input of I/O interface, it is recommended to place 0.1uF or 1uF capacitance to ground close to the chip.                                                                    |  |

| 22                                                         | DVDDK        | Р     | The external 0.1uF or 1uF capacitor to ground is placed close to the chip.                                                                                                                |  |

| 3、9、14、16、19、<br>29、48                                     | GND          | Р     | Analog ground.                                                                                                                                                                            |  |

| 7、10、11、12、13、<br>15、17、18、23、<br>38、39、40、41、<br>42、46、47 | NC           | -     | Reserved, it is recommended to float.                                                                                                                                                     |  |

| 24                                                         | LED_SPD      | Ο     | Network speed indicator LED:<br>Low level indicates 100Mbps,<br>high level indicates 10Mbps.                                                                                              |  |

| 25                                                         | LED_LIN<br>K | 0     | Network connection indication LED:<br>Low level indicates connected,<br>high level indicates not connected.                                                                               |  |

| 26                                                         | LED_DUP      | О     | Duplex indicator LED:<br>Low level indicates full-duplex,<br>high level indicates half-duplex.                                                                                            |  |

| 27                                                         | LED_ACT      | 0     | Carrier induction indicator LED:<br>Low level indicates that there is a carrier induction signal,<br>high level indicates that there is no carrier induction signal.                      |  |

| 30                                                         | XI           | Ι     | Crystal oscillator input requires an external 25MHz crystal end<br>or an external clock input.                                                                                            |  |

| 31                                                         | XO           | Ο     | The inverted output of crystal oscillator needs to be externally connected to the other end of 25MHz crystal.                                                                             |  |

| 32                                                         | SCS          | I, PU | SPI chip select input, active low.                                                                                                                                                        |  |

| 33                                                         | SCK          | Ι     | SPI clock input, supporting mode 0 or 3.                                                                                                                                                  |  |

## Table 4-1 CH394Q pin definition

| 34 | SDO   | О     | SPI serial data output, connected to MISO of SPI host of processor. |                                     |  |

|----|-------|-------|---------------------------------------------------------------------|-------------------------------------|--|

| 35 | SDI   | Ι     | SPI serial data input, connected to MOSI of SPI host of processor.  |                                     |  |

| 36 | INT   | 0     | Interrupt request output, active low.                               |                                     |  |

| 37 | RSTB  | I, PU | Reset input, active                                                 | low.                                |  |

|    |       |       | PHY operation mo                                                    | de selection                        |  |

| 43 | PMOD2 | I, PU | PMOD[2:0]                                                           | Description                         |  |

|    |       |       |                                                                     | 10M half-duplex, auto-negotiation   |  |

|    |       | I, PU | 000                                                                 | disabled.                           |  |

| 44 | PMOD1 |       | 001                                                                 | 10M full-duplex, auto-negotiation   |  |

|    |       |       |                                                                     | disabled.                           |  |

|    |       |       | 010                                                                 | 100M half-duplex, auto-negotiation  |  |

|    |       |       |                                                                     | disabled.                           |  |

|    |       |       |                                                                     | 100M full-duplex, auto-negotiation  |  |

|    |       |       | 011                                                                 | closed.                             |  |

| 45 |       |       | 100                                                                 | 100M half-duplex, auto-negotiation  |  |

| 45 | PMOD0 | I, PU | 100                                                                 | enabled.                            |  |

|    |       |       | 101                                                                 | Reserved                            |  |

|    |       |       | 110                                                                 | Reserved                            |  |

|    |       |       | 111                                                                 | Start auto-negotiation (Recommended |  |

|    |       |       |                                                                     | default mode)                       |  |

Note 1: I = Input; O = Output; I/O = Input/Output;

P = Power supply; PU = Built-in pull-up resistor.

## 5. CH394Q Data Format

The data in this manual have a suffix of B for binary numbers and H for hexadecimal numbers, otherwise they are decimal numbers.

## **5.1 Operation Mode**

CH394Q can share the SPI interface with other SPI devices. The peripheral host only needs to pull down the SCS pin to communicate with CH394Q. The interface can be used by other devices during non-communication period.

## 5.2 Data Frame

#### 5.2.1 Data Frame Format

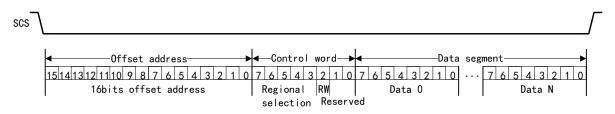

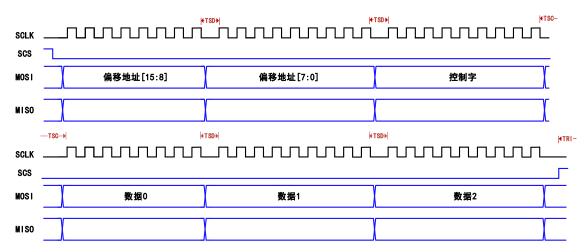

The CH394Q data frame consists of three parts: A 16-bit offset address, an 8-bit control word, and an N-byte data segment.

The offset address is the CH394Q register address or the offset address of the RX/TX buffer.

The control word is used to define the ownership of the offset area set in the address segment and determine the read/write mode.

Pulling SCS low indicates the start of a new data frame, and pulling SCS high indicates the end of a data frame.

#### Figure 5-1 CH394Q data frame

CH394Q supports continuous reading or writing of data, starting from the starting address. After each transmission of data at an offset address, the offset address will automatically increase by 1 to transmit the next data.

#### 5.2.2 Control Phase

The CH394Q control phase specifies:

1. Ownership of the offset area set in the address segment;

2. SPI read/write mode;

| Bit   | Name                             | Description                                                                                                                                                                                                                                      |               |                 |  |  |  |

|-------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|--|--|--|

| [7:3] | BS                               | <ul><li>Block selection bits:</li><li>Used to define the ownership of the offset area set in the addre segment.</li><li>CH394Q contains 1 common register, 8 socket registers, and th corresponding socket read and write buffer area.</li></ul> |               |                 |  |  |  |

|       |                                  | BS [7:3                                                                                                                                                                                                                                          | 3]            |                 |  |  |  |

|       | Segment number<br>selection[7:5] | Segment number<br>selection[7:5]                                                                                                                                                                                                                 | Function[4:3] | Description     |  |  |  |

|       |                                  | 000                                                                                                                                                                                                                                              | 00            | Common register |  |  |  |

|       |          | 000                     | 01   | Socket 0 register  |  |  |

|-------|----------|-------------------------|------|--------------------|--|--|

|       |          | 000                     | 10   | Socket 0 TX buffer |  |  |

|       |          | 000                     | 11   | Socket 0 RX buffer |  |  |

|       |          | 001                     | 00   | Meaningless        |  |  |

|       |          | 001                     | 01   | Socket 1 register  |  |  |

|       |          | 001                     | 10   | Socket 1 TX buffer |  |  |

|       |          | 001                     | 11   | Socket 1 RX buffer |  |  |

|       |          | 010                     | 00   | Meaningless        |  |  |

|       |          | 010                     | 01   | Socket 2 register  |  |  |

|       |          | 010                     | 10   | Socket 2 TX buffer |  |  |

|       |          | 010                     | 11   | Socket 2 RX buffer |  |  |

|       |          | 011                     | 00   | Meaningless        |  |  |

|       |          | 011                     | 01   | Socket 3 register  |  |  |

|       |          | 011                     | 10   | Socket 3 TX buffer |  |  |

|       |          | 011                     | 11   | Socket 3 RX buffer |  |  |

|       |          | 100                     | 00   | Meaningless        |  |  |

|       |          | 100                     | 01   | Socket 4 register  |  |  |

|       |          | 100                     | 10   | Socket 4 TX buffer |  |  |

|       |          | 100                     | 11   | Socket 4 RX buffer |  |  |

|       |          | 101                     | 00   | Meaningless        |  |  |

|       |          | 101                     | 01   | Socket 5 register  |  |  |

|       |          | 101                     | 10   | Socket 5 TX buffer |  |  |

|       |          | 101                     | 11   | Socket 5 RX buffer |  |  |

|       |          | 110                     | 00   | Meaningless        |  |  |

|       |          | 110                     | 01   | Socket 6 register  |  |  |

|       |          | 110                     | 10   | Socket 6 TX buffer |  |  |

|       |          | 110                     | 11   | Socket 6 RX buffer |  |  |

|       |          | 111                     | 00   | Meaningless        |  |  |

|       |          | 111                     | 01   | Socket 7 register  |  |  |

|       |          | 111                     | 10   | Socket 7 TX buffer |  |  |

|       |          | 111                     | 11   | Socket 7 RX buffer |  |  |

|       |          | Read/write selection b  | oit: |                    |  |  |

| 2     | RW       | 0: SPI read;            |      |                    |  |  |

|       |          | 1: SPI write.           |      |                    |  |  |

| [1:0] | Reserved | Reserved, default is 0. |      |                    |  |  |

## **5.3 Data Frame Example**

The CH394Q registers use big-end mode for data storage. In memory, the low byte is placed in the high address bit while the high byte is located in the low address bit.

## 5.3.1 Data Frame Example

(1) Read 2-byte data

Read 2-byte of unreachable port information from the common register (Assuming the unreachable port is 0x03e8):

MOSI: 0x00,0x2c,0x00,0x00,0x00 MISO: - ,- ,- ,0x03,0xe8 (2) Write 6-byte data Configure the Socket5 destination MAC as 0x11:0x22:0x33:0x44:0x55:0x66: MOSI: 0x00,0x06,0xac,0x11,0x22,0x33,0x44,0x55,0x66 MISO: - ,- ,- ,- ,- ,- ,- ,- ,- ,-

## 6. CH394Q Register and Buffer

CH394Q has 1 common register area, 8 socket register areas, 8 receive buffer areas and 8 transmit buffer areas.

There are multiple configurable registers in each register area. Each register in the same area has a different offset address. The register to be read or written is determined by the different offset addresses in the address segment. The BS bit of the control word is used to define which register area the offset address set in the address segment belongs to.

CH394Q has a total of 16K transmit buffer, 8 sockets each default 2K; 16K receive buffer, 8 sockets each default 2K.

When reading/writing the socket receive/transmit buffer, the offset address in the address segment (Obtained by querying the RD/WR register) represents the starting address of the data storage, and the BS bit in the control word controls the specific receive/transmit buffer to be read/written.

## 6.1 Register Table

#### 6.1.1 Common Register Table

The CH394Q common register configures the CH394Q mode, IP, MAC, etc. To read/write the common register, you need to fill in the offset address corresponding to the register in the offset address part of the data frame, and set the BS part of the control word to 00000B.

| Offset address | Name   | Access | Description                       | Reset value |

|----------------|--------|--------|-----------------------------------|-------------|

| 0x0000         | MODE   | RW     | Mode register                     | 0x00        |

| 0x0001         | GWIP0  |        |                                   | 0x00        |

|                |        | RW     | Gateway address register          |             |

| 0x0004         | GWIP3  |        |                                   | 0x00        |

| 0x0005         | SMIP0  |        |                                   | 0x00        |

|                |        | RW     | Subnet mask register              |             |

| 0x0008         | SMIP3  |        |                                   | 0x00        |

| 0x0009         | MAC0   |        |                                   | 0xXX        |

|                |        | RW     | MAC address register              |             |

| 0x000E         | MAC5   |        |                                   | 0xXX        |

| 0x000F         | IP0    |        |                                   | 0x00        |

|                |        | RW     | Source IP address register        |             |

| 0x0012         | IP3    |        |                                   | 0x00        |

| 0x0013         | IIT0   | RW     | Interment interval times assisted | 0x00        |

| 0x0014         | IIT1   | ĸw     | Interrupt interval time register  | 0x00        |

| 0x0015         | GINT   | RW     | Global interrupt register         | 0x00        |

| 0x0016         | GINTE  | RW     | Global interrupt enable register  | 0x00        |

| 0x0017         | SINT   | RO     | Socket interrupt register         | 0x00        |

| 0x0018         | SINTE  | RW     | Socket interrupt enable register  | 0x00        |

| 0x0019         | RTIME0 | DW     | Define entire in the entire       | 0x07        |

| 0x001A         | RTIME1 | RW     | Retransmission time register      | 0xD0        |

| 0x001B         | RCNT   | RW     | Retransmission count register     | 0x08        |

| 0x001C         | -      | -      | Reserved                          | -           |

Table 6-1 Common register table

| 0x0027 |         |    |                            |      |

|--------|---------|----|----------------------------|------|

| 0x0028 | UNIP0   |    |                            | 0x00 |

|        |         | RO | Unreachable IP register    |      |

| 0x002B | UNIP3   |    |                            | 0x00 |

| 0x002C | UNPORT0 | RO | Unreachable port register  | 0x00 |

| 0x002D | UNPORT1 | KU |                            | 0x00 |

| 0x002E | PHY_CFG | RW | PHY configuration register | 0xB8 |

| 0x002F |         |    |                            |      |

|        | -       | -  | Reserved                   | -    |

| 0x0038 |         |    |                            |      |

| 0x0039 | CHIPV   | RO | Chip version register      | 0xXX |

### 6.1.2 Socket Register Table

CH394Q provides 8 Sockets, each Socket corresponds to a Socket register area, the register area corresponding to Socket n ( $0 \le n \le 7$ ) is selected by the BS bit of the control word (Refer to 5.2.2 for details), and the register of Socket n to be read/written is determined by the offset address.

| Offset address | Name          | Access                                | Description                            | Reset value |

|----------------|---------------|---------------------------------------|----------------------------------------|-------------|

| 0x0000         | Sn_MODE       | RW                                    | Socket n mode register                 | 0x00        |

| 0x0001         | Sn_CTRL       | RW                                    | Socket n control register              | 0x00        |

| 0x0002         | Sn_INT        | RW                                    | Socket n interrupt register            | 0x00        |

| 0x0003         | Sn_STA        | RO                                    | Socket n status register               | 0x00        |

| 0x0004         | Sn_PORT0      | RW                                    |                                        | 0x00        |

| 0x0005         | Sn_PORT1      | KW                                    | Socket n source port register          | 0x00        |

| 0x0006         | Sn_DMAC0      |                                       |                                        | 0x00        |

|                |               | RW                                    | Socket n destination MAC register      |             |

| 0x000B         | Sn_DMAC5      |                                       |                                        | 0x00        |

| 0x000C         | Sn_DIP0       |                                       |                                        | 0x00        |

|                |               | RW                                    | Socket n destination IP register       |             |

| 0x000F         | Sn_DIP3       |                                       |                                        | 0x00        |

| 0x0010         | Sn_DPORT0     | RW Socket n destination port register |                                        | 0x00        |

| 0x0011         | Sn_DPORT1     | KW                                    | Socket in destination port register    | 0x00        |

| 0x0012         | Sn_MTU0       | RW                                    | Socket n maximum transfer unit         | 0x00        |

| 0x0013         | Sn_MTU1       | KW                                    | register                               | 0x00        |

| 0x0014         | -             | -                                     | Reserved                               | -           |

| 0x0015         | Sn_TOS        | RW                                    | Socket n IP service type register      | 0x00        |

| 0x0016         | Sn_TTL        | RW                                    | Socket IP time-to-live register        | 0x80        |

| 0x0017         |               |                                       |                                        |             |

|                | -             | -                                     | Reserved                               | -           |

| 0x001D         |               |                                       |                                        |             |

| 0x001E         | Sn_RXBUF_SIZE | RW                                    | Socket n receive buffer size register  | 0x02        |

| 0x001F         | Sn_TXBUF_SIZE | RW                                    | Socket n transmit buffer size register | 0x02        |

| 0x0020         | Sn_TX_FS0     | RO                                    | Socket n idle transmit buffer length   | 0x08        |

| 0x0021 | Sn_TX_FS1    |    | register                               | 0x00 |

|--------|--------------|----|----------------------------------------|------|

| 0x0022 | Sn_TX_RD0    | RO | Socket n transmit buffer read pointer  | 0xXX |

| 0x0023 | Sn_TX_RD1    | KO | register                               | υχλλ |

| 0x0024 | Sn_TX_WR0    | RW | Socket n transmit buffer write pointer | 0xXX |

| 0x0025 | Sn_TX_WR1    |    | register                               | ΟΧΛΛ |

| 0x0026 | Sn_RX_RS0    | RO |                                        |      |

| 0x0027 | Sn_RX_RS1    | KO | Socket n receive data length register  | 0x00 |

| 0x0028 | Sn_RX_RD0    | RW | Socket n receive buffer read pointer   | 0xXX |

| 0x0029 | Sn_RX_RD1    | KW | register                               | UXAA |

| 0x002A | Sn_RX_WR0    | RO | Socket n receive buffer write pointer  | 0xXX |

| 0x002B | Sn_RX_WR1    | KO | register                               | UXAA |

| 0x002C | Sn_INTE      | RW | Socket n interrupt enable register     | 0xFF |

| 0x002D | Sn_IPF0      | RW | Socket a ID for growt as gister        | 0x40 |

| 0x002E | Sn_IPF1      |    | Socket n IP fragment register          | 0x00 |

| 0x002F | Sn_KEEPALIVE | RW | Socket n KeepAlive time register       | 0x00 |

## 6.2 RX/TX Buffer

| 0x3FFF   |                                 | 0x3FFF 🖛 |                                |

|----------|---------------------------------|----------|--------------------------------|

| 0x3FFF   | Socket7 transmit<br>buffer(2KB) | 0x3800   | Socket7 receive<br>buffer(2KB) |

| 0x3000   | Socket6 transmit<br>buffer(2KB) | 0x3000   | Socket6 receive<br>buffer(2KB) |

| 0x2800   | Socket5 transmit<br>buffer(2KB) | 0x2800   | Socket5 receive<br>buffer(2KB) |

| 0x2000   | Socket4 transmit<br>buffer(2KB) | 0x2000   | Socket4 receive<br>buffer(2KB) |

| 0x2000   | Socket3 transmit<br>buffer(2KB) | 0x1800   | Socket3 receive<br>buffer(2KB) |

| 0x1800   | Socket2 transmit<br>buffer(2KB) | 0x1800   | Socket2 receive<br>buffer(2KB) |

| 0x0800   | Socket1 transmit<br>buffer(2KB) |          | Socket1 receive<br>buffer(2KB) |

|          | Socket0 transmit<br>buffer(2KB) | 0×0800 - | SocketO receive<br>buffer(2KB) |

| 0x0000 I |                                 | 0×0000 └ |                                |

### Figure 6-1 RX/TX buffer

16K Socket receive buffer

16K Socket transmit buffer

Each socket (n =  $0 \sim 7$ ) of bit CH394Q provides an independent transmitting and receiving memory buffer, with a total of 16K receiving buffer and 16K transmitting buffer.

In the initial state, the transmitting and receiving buffers of each Socket are allocated to 2KB (The receiving buffer is 16KB in total and the transmitting buffer is 16KB in total). Users can reallocate the 16KB memory resources to each Socket by configuring the Socket transmit buffer size register (Sn\_TXBUF\_SIZE) and the Socket receive buffer size register (Sn\_RXBUF\_SIZE) as required, but it is necessary to ensure that the sum of the receive buffer and transmit buffer sizes of all sockets does not exceed 16KB to prevent data transmission errors.

## 7. CH394Q Register Description

Socket Pair contains a quadruple of source IP, source port, destination IP and destination port, which can uniquely identify the two connected parties in the Internet. This manual is referred to as Socket for short. CH394Q can provide 8 Socket at the same time, and their index values are 0, 1, 2, 3 ....

The high and low bytes of IP and MAC addresses agreed in this manual may be different from some documents, just for convenience:

For example, the IP address is 192.168.1.2, where 192 is the highest byte and 2 is the lowest byte.

For example, the MAC address is 0x11:0x22:0x33:0x44:0x55:0x66, where 0x11 is the highest byte and 0x66 is the lowest byte.

## 7.1 Common Register Description

CH394Q register uses big terminal mode for data storage. In memory, the low byte is placed in the high address bit, while the high byte is placed in the low address bit.

## 7.1.1 Mode Register (MODE) [0x0000]

This register is used to control the operation mode.

| Bit | Name     | Description                                                                                                                                                                                                                                                                                                  | Access | Default value |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | RST      | Set 1 for software reset, and it will be cleared automatically after the reset is completed.                                                                                                                                                                                                                 | RW, SC | 0             |

| 6   | Reserved | Reserved                                                                                                                                                                                                                                                                                                     | RO     | 0             |

| 5   | WOL      | <ul> <li>Wake on LAN enabled:</li> <li>0: Disable WOL mode;</li> <li>1. Enable WOL mode.</li> <li>CH394Q integrates the magic packet WOL mode. After enabling the magic packet wake-up, CH394Q will pull down the INT pin after receiving the magic packet (0xFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF</li></ul> | RW     | 0             |

| 4   | РВ       | PING packet block enabled:<br>0: Disable PING block;<br>1: Enable PING block.                                                                                                                                                                                                                                | RW     | 0             |

| 3   | Reserved | Reserved                                                                                                                                                                                                                                                                                                     | RO     | 0             |

| 2   | Reserved | Reserved                                                                                                                                                                                                                                                                                                     | RO     | 0             |

| 1   | FARP     | <ul> <li>Forced ARP enable:</li> <li>0: Disable forced ARP mode;</li> <li>1: Enable forced ARP mode.</li> <li>Turn on forced ARP mode. When forced ARP is turned on, an ARP request will be forced to be sent before each UDP packet is sent.</li> </ul>                                                     | RW     | 0             |

| 0   | Reserved | Reserved                                                                                                                                                                                                                                                                                                     | RO     | 0             |

#### Table 7-1 Mode Register

#### 7.1.2 Gateway IP Address Register (GWIP) [0x0001-0x0004]

This register is used to set the gateway address, and the low byte address stores the high byte of the gateway address. For example: The gateway IP is 192.168.1.1.

| Address | 0x0001 | 0x0002 | 0x0003 | 0x0004 |

|---------|--------|--------|--------|--------|

| Data    | 0xC0   | 0xA8   | 0x01   | 0x01   |

### 7.1.3 Subnet Mask IP Address Register (SMIP) [0x0005-0x0008]

This register is used to set the subnet mask address, and the low byte address stores the high byte of the subnet mask address.

For example: Subnet mask IP 255.255.255.0

| Address | 0x0005 | 0x0006 | 0x0007 | 0x0008 |

|---------|--------|--------|--------|--------|

| Data    | 0xFF   | 0xFF   | 0xFF   | 0x00   |

## 7.1.4 MAC Address Register (MAC) [0x0009-0x000E]

This register is used to set the MAC address of CH394Q, and the low byte address stores the high byte of the MAC address.

The CH394Q chip has burned the MAC address assigned by IEEE when it leaves the factory. Please do not set the MAC address unless it is necessary.

For example: The MAC address is 0x38:0x3B:0x26:0x11:0x22:0x33

| Address | 0x0009 | 0x000A | 0x000B | 0x000C | 0x000D | 0x000E |

|---------|--------|--------|--------|--------|--------|--------|

| Data    | 0x38   | 0x3B   | 0x26   | 0x11   | 0x22   | 0x33   |

## 7.1.5 Source IP Address Register (IP) [0x000F-0x0012]

This register is used to set the IP address of CH394Q, and the low byte address stores the high byte of the IP address. For example: The source address is 192.168.1.100

| Address | 0x000F | 0x0010 | 0x0011 | 0x0012 |

|---------|--------|--------|--------|--------|

| Data    | 0xC0   | 0xA8   | 0x01   | 0x64   |

## 7.1.6 Interrupt Interval Register (IIT) [0x0013-0x0014]

This register is used to set the waiting time for the interrupt to take effect, and the default value is 0. When an interrupt event is handled, the INT signal line will return to high level, and it will take a set IIT interval time before CH394Q will notify the next interrupt and pull the INT signal line low.

The formula for calculating the interval time is: Time = 1/12000000\*4\*(IIT+1).

For example, if the register value is set to 1000, then the interval time is about 33.3us

| Address | 0x0013 | 0x0014 |

|---------|--------|--------|

| Data    | 0x03   | 0xE8   |

## 7.1.7 Global Interrupt Register (GINT) [0x0015]

This register is used to obtain the global interrupt status. When an interrupt event occurs, the corresponding bit in the GINT register will be set to 1. Writing a 1 to this bit can clear the interrupt flag bit. If the enable bit of this interrupt in GINTE is also 1, the level of the INT pin becomes low. Thereafter, once the corresponding bit of the event is cleared or the corresponding interrupt enable bit is set to 0, and the SINT is 0, the INT pin is restored to high level.

| Bit   | Name          | Description                                                                                                                                                                                                                                                                                                                                                                  | Access | Default value |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7     | IP_CONFL<br>I | IP conflict interrupt:<br>This interrupt occurs when CH394Q detects that its<br>own IP address is the same as that of other network<br>devices in the same network segment.                                                                                                                                                                                                  | RW     | 0             |

| 6     | UNREACH       | Unreachable interrupt:<br>When CH394Q receives the ICMP unreachable<br>interrupt message, it saves the IP address, port and<br>protocol type of the unreachable IP packet in the<br>unreachable information table, and then generates this<br>interrupt.<br>After receiving this interrupt, MCU can query UNIP<br>and UNPORT registers to obtain unreachable<br>information. | RW     | 0             |

| 5     | Reserved      | Reserved                                                                                                                                                                                                                                                                                                                                                                     | RO     | 0             |

| 4     | MP            | Magic packet wake-up interrupt:<br>This interrupt occurs when the Magic Packet function<br>is enabled and the Magic Packet WOL mode is received<br>through UDP.                                                                                                                                                                                                              | RW     | 0             |

| [3:0] | Reserved      | Reserved                                                                                                                                                                                                                                                                                                                                                                     | RO     | 0             |

| Table 7-2 | Global | interru | ot register |

|-----------|--------|---------|-------------|

|           | Global | muchu   | JUICEISICI  |

## 7.1.8 Global Interrupt Enable Register (GINTE) [0x0016]

This register is used to control which interrupt sources can trigger interrupts, and each interrupt event enable bit corresponds to one bit of the global interrupt register (GINT).

When the interrupt event is generated, only when the corresponding bit in GINTE is 1, CH394Q will pull down the INT pin and generate an interrupt.

| Bit   | Name          | Description                                                                                                               | Access | Default value |

|-------|---------------|---------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7     | IP_CONFL<br>I | IP conflict interrupt enable bit:<br>Enable this bit allows IP collision interrupts to be<br>generated.                   | RW     | 0             |

| 6     | UNREACH       | Unreachable interrupt enable bit:<br>Enable this bit allows unreachable interrupts to be<br>generated.                    | RW     | 0             |

| 5     | Reserved      | Reserved                                                                                                                  | RO     | 0             |

| 4     | MP            | Magic Packet Wake-up Interrupt Enable Bit:<br>Enable this bit allows the generation of Magic Packet<br>Wake-up Interrupt. | RW     | 0             |

| [3:0] | Reserved      | Reserved                                                                                                                  | RO     | 0             |

Table 7-3 Global interrupt enable register

## 7.1.9 Socket Interrupt Register (SINT) [0x0017]

This register is used to obtain the socket interrupt status. When an interrupt event occurs on socket n, the corresponding bit of the Sn INT register will be 1 and the nth bit of SINT will be 1, and the INT pin will be pulled

low. When Sn\_INT is 0, the corresponding bit of SINT will also be cleared. The INT pin is pulled high when both SINT and GINT are '0x00'.

| Bit | Name   | Description       | Access | Default value |

|-----|--------|-------------------|--------|---------------|

| 7   | S7_INT | Socket7 interrupt | RO     | 0             |

| 6   | S6_INT | Socket6 interrupt | RO     | 0             |

| 5   | S5_INT | Socket5 interrupt | RO     | 0             |

| 4   | S4_INT | Socket4 interrupt | RO     | 0             |

| 3   | S3_INT | Socket3 interrupt | RO     | 0             |

| 2   | S2_INT | Socket2 interrupt | RO     | 0             |

| 1   | S1_INT | Socket1 interrupt | RO     | 0             |

| 0   | S0_INT | Socket0 interrupt | RO     | 0             |

Table 7-4 Socket interrupt register

## 7.1.10 Socket Interrupt Enable Register (SINTE) [0x0018]

This register is used to control which Sockets can trigger interrupts, and each enable bit corresponds to one bit of the socket interrupt register (SINT).

When the Socket interrupt event is generated, only when the corresponding bit in SINTE is 1, CH394Q will pull down the INT pin and generate an interrupt.

| Bit | Name   | Description                                                                                         | Access | Default value |

|-----|--------|-----------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | S7_INT | Socket7 interrupt enable bit:<br>Enabling this bit allows the generation of Socket 7<br>interrupts. | RW     | 0             |

| 6   | S6_INT | Socket6 interrupt enable bit:<br>Enabling this bit allows the generation of Socket 6<br>interrupts. | RW     | 0             |

| 5   | S5_INT | Socket5 interrupt enable bit:<br>Enabling this bit allows the generation of Socket 5<br>interrupts. | RW     | 0             |

| 4   | S4_INT | Socket4 interrupt enable bit:<br>Enabling this bit allows the generation of Socket 4<br>interrupts. | RW     | 0             |

| 3   | S3_INT | Socket3 interrupt enable bit:<br>Enabling this bit allows the generation of Socket 3<br>interrupts. | RW     | 0             |

| 2   | S2_INT | Socket2 interrupt enable bit:<br>Enabling this bit allows the generation of Socket 2<br>interrupts. | RW     | 0             |

| 1   | S1_INT | Socket1 interrupt enable bit:<br>Enabling this bit allows the generation of Socket 1<br>interrupts. | RW     | 0             |

| 0   | S0_INT | Socket0 interrupt enable bit:<br>Enabling this bit allows the generation of Socket 0                | RW     | 0             |

Table 7-5 Socket interrupt enable register

|  | intownsets  |  |

|--|-------------|--|

|  | interrubts. |  |

|  |             |  |

|  |             |  |

#### 7.1.11 Retransmission Time Register (RTIME) [0x0019-0x001A]

This register is used to set the retransmission time in TCP communication and the retransmission time of ARP. If TCP transmission or ARP request does not receive a response from the other party within the RTIME time, a retransmission operation will be performed or a timeout interrupt will be triggered.

RTIME requires a two-byte time value with a unit of 0.1ms. The default value is 2000 (0x07D0), i.e. 200ms (2000\*0.1ms). Note that the RTIME value must be a multiple of 1000.

For example: Set retransmission time as 5000 (0x1388), i.e. 500ms.

| Address | 0x0019 | 0x001A |

|---------|--------|--------|

| Data    | 0x13   | 0x88   |

#### 7.1.12 Retransmission Count Register (RCN) [0x001B]

This register is used to set the retransmission timeout count. The retransmission timeout count refers to the maximum number of times a packet is retransmitted without a response, and the default value is 8. When the retransmission exceeds the set number of times, the corresponding socket timeout interrupt bit will be set to 1.

#### 7.1.13 Unreachable IP Register (UNIP) [0x0028-0x002B]

This register is used to obtain an unreachable IP address. When CH394Q transmits data to an unreachable port, the other party will reply with an ICMP packet (Destination port unreachable). After receiving the unreachable message, CH394Q will generate an unreachable interrupt. The microcontroller can use this command to obtain the unreachable address.

For example: Unreachable IP is 192.168.1.200

| Address | 0x0028 | 0x0029 | 0x002A | 0x002B |

|---------|--------|--------|--------|--------|

| Data    | 0xC0   | 0xA8   | 0x01   | 0xC8   |

#### 7.1.14 Unreachable Port Register (UNPORT) [0x002C-0x002D]

This register is used to obtain an unreachable port. When CH394Q transmits data to an unreachable port, the other party will reply with an ICMP packet (Destination port unreachable). After receiving the unreachable message, CH394Q will generate an unreachable interrupt. The microcontroller can use this command to obtain the unreachable port.

For example: Unreachable Port is 2000

| Address | 0x002C | 0x002D |

|---------|--------|--------|

| Data    | 0x07   | 0xD0   |

#### 7.1.15 PHY Configuration Register (PHY\_CFG) [0x002E]

This register configures status of PHY, and it indicates the current PHY connection status.

| Bit | Name | Description                                                                                                     | Access | Default value |

|-----|------|-----------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | RST  | Reset:<br>0: PHY reset;<br>1: Normal work.<br><i>Note: This bit needs to be set to 1 manually after the PHY</i> | RW     | 1             |

#### Table 7-6 PHY configuration register

|       |       | reset is comp                                                                                                                         | leted                                      |      |     |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|-----|

|       |       |                                                                                                                                       | bde selection bit:                         |      |     |

|       |       | -                                                                                                                                     | the PHY mode through hardware pin          | s    |     |

|       |       | (PMOD[2:0])                                                                                                                           |                                            |      |     |

|       |       |                                                                                                                                       | the PHY mode via the PHY Configuratio      | n    |     |

|       |       | Register [5:3                                                                                                                         |                                            |      |     |

|       |       |                                                                                                                                       | 4Q is powered on or reset by RSTB pin,     | t    |     |

|       |       |                                                                                                                                       | vel status of PMOD[2:0] pin to set the PHY |      |     |

|       |       | operation mo                                                                                                                          |                                            |      |     |

| 6     | OPWD  | -                                                                                                                                     | er wants to control the PHY mode throug    | RW   | 0   |

|       |       |                                                                                                                                       | s necessary to:                            |      |     |

|       |       |                                                                                                                                       | OPWD as 1;                                 |      |     |

|       |       |                                                                                                                                       | OPMDC to the desired mode value.           |      |     |

|       |       |                                                                                                                                       | ser wants to use the level state of th     | e    |     |

|       |       |                                                                                                                                       | bin to set the PHY operation mode again, h |      |     |

|       |       |                                                                                                                                       | o set the OPWD bit from 1 to 0 withou      |      |     |

|       |       | -                                                                                                                                     | or resetting it again.                     |      |     |

|       |       |                                                                                                                                       |                                            |      |     |

|       |       | [5:3]                                                                                                                                 | Description                                |      |     |

|       |       | []                                                                                                                                    | 10M half-duplex, auto-negotiation          |      |     |

|       |       | disabled                                                                                                                              |                                            |      |     |

|       |       |                                                                                                                                       | 10M full-duplex, auto-negotiation          |      |     |

|       |       | 001                                                                                                                                   | disabled                                   |      |     |

|       |       |                                                                                                                                       | 100M half-duplex, auto-negotiation         |      |     |

|       |       | OPMDC     010     disabled       011     100M full-duplex, auto-negotiation disabled       100     100M half-duplex, auto-negotiation | RW                                         | 111b |     |

| [5:3] | OPMDC |                                                                                                                                       |                                            |      |     |

|       |       |                                                                                                                                       |                                            |      | l   |

|       |       |                                                                                                                                       |                                            |      |     |

|       |       |                                                                                                                                       | enabled                                    |      |     |

|       |       | 101                                                                                                                                   | Reserved                                   |      |     |

|       |       | 110                                                                                                                                   | Power-down mode                            |      |     |

|       |       | 111                                                                                                                                   | Enable auto-negotiation                    |      |     |

|       |       |                                                                                                                                       | onfiguration bit                           |      |     |

|       |       | Duplex status                                                                                                                         |                                            |      |     |

| 2     | DUPS  | 0: half-duplex                                                                                                                        |                                            | RO   | 0   |

| -     |       | 1: full-duplex                                                                                                                        |                                            |      | U   |

|       |       |                                                                                                                                       |                                            |      |     |

| 1     | SPDS  | Speed status<br>0: 10Mb/s;                                                                                                            |                                            | RO   | 0   |

| -     | ~     | 1: 100Mb/s.                                                                                                                           |                                            |      | -   |

|       |       | Link status                                                                                                                           |                                            |      |     |

| 0     | LINKS |                                                                                                                                       | al layer does not establish a link;        | RO   | 0   |

| Ŭ     |       |                                                                                                                                       | al layer establishes the link.             |      | , v |

|       | _     |                                                                                                                                       | J                                          |      | l   |

## 7.1.16 Chip Version Register (CHIPV) [0x0039]

This register is used to obtain the chip version.

## 7.2 Socket Register Description

## 7.2.1 Socket n Mode Register (Sn\_MODE) [0x0000]

This register is used to configure the operation mode of Socket n.

| Bit | Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Access | Default value |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | MUL_MFE<br>N | <ul> <li>When Socket n works in UDP mode:</li> <li>0: Disable multicast mode;</li> <li>1: Enable multicast mode.</li> <li>When using multicast mode, you need to configure the multicast IP, multicast MAC, and port number through Sn_DIP and Sn_DPORT in advance before the socket is opened.</li> <li>When Socket n is operating in MAC RAW mode:</li> <li>0: Disables MAC address filtering;</li> <li>1: Enables MAC address filtering.</li> <li>When MAC RAW mode is used, with MAC address filtering turned on, Socket n will only receive packets on the network whose destination MAC is the CH394Q's own MAC address as well as the broadcast address.</li> </ul>                                                                                  | RW     | 0             |

| 6   | BCASTB       | <ul><li>Broadcast blocking shielding bit:</li><li>0: Disable broadcast blocking;</li><li>1: Enable broadcast blocking.</li><li>After this position 1, in UDP and MAC RAW mode,</li><li>Socket n will not receive broadcast blocking on the network.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RW     | 0             |

| 5   | NA_MV_M<br>M | <ul> <li>When Socket n is operating in TCP mode:</li> <li>0: Disable no-delay ACK;</li> <li>1: Enable no-delay ACK.</li> <li>After enabling no-delay ACK, Socket n will reply to</li> <li>ACK as soon as possible after receiving the packet from</li> <li>the opposite end without delay; otherwise, it will wait</li> <li>for 10ms before replying to ACK.</li> <li>When Socket n is operating in UDP multicast mode:</li> <li>0: Use IGMP version 2;</li> <li>1: Use IGMP version 1.</li> <li>When Socket n is operating in MAC RAW mode:</li> <li>0: Disable multicast blocking;</li> <li>1: Enable multicast blocking.</li> <li>When this position is set to 1, in MACRAW mode,</li> <li>Socket n will not receive multicast packets on the</li> </ul> | RW     | 0             |

network.

| 4       UCASTB_       When Socket n is operating in UDP multicast mode:         4       UCASTB_       Socket n will not receive unicast packets on the network. | 0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 4 UCASTB 1: Enable unicast blocking.<br>UCASTB RW                                                                                                               | 0 |

| 4 When this position is set to 1, in UDP multicast mode,<br>Socket n will not receive unicast packets on the<br>network. RW                                     | 0 |

| 4 UCASTB Socket n will not receive unicast packets on the network. RW                                                                                           | 0 |

| 4 UCASTB_ network. RW                                                                                                                                           | 0 |

| A network. RW                                                                                                                                                   | 0 |

|                                                                                                                                                                 |   |

| MIP6B When Socket n is working in MAC RAW mode:                                                                                                                 |   |

| 0: Disable IPv6 blocking;                                                                                                                                       |   |

| 1: Enable IPv6 blocking.                                                                                                                                        |   |

| After this position 1, in MAC RAW mode, Socket n                                                                                                                |   |

| will not receive IPv6 packets on the network.                                                                                                                   |   |

| Set Socket operation mode:                                                                                                                                      |   |

| [3:0] Description                                                                                                                                               |   |

| 0000 OFF                                                                                                                                                        |   |

| [3:0] PMD 0001 TCP RW                                                                                                                                           | 0 |

| 0010 UDP                                                                                                                                                        |   |

| 0100 MAC RAW                                                                                                                                                    |   |

| Note: Only Socket 0 can use MAC RAW mode.                                                                                                                       |   |

## 7.2.2 Socket n Control Register (Sn\_CTRL) [0x0001]

This register is used to set the control command of Socket n. After configuring this register, the register will be automatically cleared. After setting the control command, the control command usually takes a certain amount of time to execute. Users can judge the command execution status through the Sn\_INT or Sn\_STA register.

|      | Table 7-8 Socket if mode register |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                             |                     |                 |

|------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------|-----------------|

| Code | Name                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Descr                                                                       | iption              |                 |

|      |                                   | can query the c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | en Socket n according t<br>ommand execution st<br>euted successfully, the c | atus through Sn_STA | A, and when the |

| 01H  | OPEN                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Sn_MODE[3:0]                                                                | Sn_STA              |                 |

|      |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0000 (OFF)                                                                  | -                   |                 |

|      |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0001 (TCP)                                                                  | 0x13 (INIT)         |                 |

|      |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0010 (UDP)                                                                  | 0x22 (UDP)          |                 |

|      |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0100 (MAC RAW)                                                              | 0x42 (MAC RAW)      |                 |

| 02H  | LISTEN                            | Set Socket n to the listening state:         This command takes effect only when Socket n is in TCP mode and is in the         INIT state.         When Socket n is set to LISTEN state, Socket n is in TCP Sever mode and waits         for the client to connect, and the Sn_STA register becomes 0x14 (LISTEN).         After the client connects successfully, the Sn_STA register value becomes 0x17         (ESTABLISHED) and Sn_INT[0] is set to 1.         If the connection fails the Sn_STA register value becomes 0x00 (CLOSE) and         Sn INT[3] is set to 1. |                                                                             |                     |                 |

| Table 7-8 Socket | n mode | register |

|------------------|--------|----------|

|------------------|--------|----------|

|       |            | Enable Socket n to enter connection mode:                                          |

|-------|------------|------------------------------------------------------------------------------------|

|       |            | This command takes effect only when Socket n is in TCP mode and is in INIT         |

|       |            | state.                                                                             |

|       |            | Enabling Socket to enter connection mode means TCP Client mode. When this          |

|       |            | command is executed, Socket n connects to the server according to the values       |

|       |            | set by Sn_DIP and Sn_DPORT, and the value of Sn_STA register changes to            |

|       |            | 0x17 (ESTABLISHED) and Sn_INT[0] is set to 1 when the connection is                |

|       |            | successful.                                                                        |

| 04H   | CONNECT    | When the socket connection fails:                                                  |

|       |            | 1: ARP failure, cannot get the destination MAC address (Sn_INT[3] set to 1);       |

|       |            | 2: Connection timeout, cannot receive SYN/ACK packet from the other party          |

|       |            | after transmitting SYN packet, after retransmission timeout (Sn_INT[3] set to      |

|       |            | 1);                                                                                |

|       |            | 3: Receiving RST packet, being disconnected by the other party on its own          |

|       |            | initiative.                                                                        |

|       |            | The Sn STA register value becomes 0x00 (CLOSE) when the above situation            |

|       |            | occurs.                                                                            |

|       |            | Socket n disconnect:                                                               |

|       | DISCONNECT | This command is effective only when Socket n is in TCP mode.                       |

|       |            | Active close: Actively transmit a FIN packet to the other end device;              |

|       |            | Passive close: After receiving a FIN packet from the other end, execute this       |

| 08H   |            | command to reply a FIN packet to the other end.                                    |

|       |            | If the FIN packet does not receive the ACK response from the other side, after     |

|       |            | the retransmission timeout, Sn INT[3] is set to 1, and the value of Sn STA         |

|       |            | register becomes 0x00(CLOSE).                                                      |

|       |            | Close Socket n:                                                                    |

|       |            | If Socket n is in UDP or MAC RAW mode, this command will directly close            |

|       |            | Socket.                                                                            |

| 10H   | CLOSE      | If Socket n is in TCP mode, this command will transmit a RST packet to close       |

|       |            | the Socket. Unlike the standard TCP closing process, this command will not         |

|       |            |                                                                                    |

|       |            | transmit a FIN packet when it is closed.                                           |

| 2011  | CENID      | Socket n transmitting data:                                                        |

| 20H   | SEND       | Transmitting the data in the Socket n transmitting buffer. See section 11.2.2 Data |

|       |            | transmitting process for details.                                                  |

|       |            | Socket n transmits data without ARP:                                               |

| 0.111 |            | This command only takes effect when Socket n is in UDP mode.                       |

| 21H   | SNED_MAC   | The SEND process is the same as the transmit command, but the MAC address          |

|       |            | of the opposite end is not obtained through ARP before the contract is sent, and   |

|       |            | the MAC address set by Sn_DMAC is used directly.                                   |

|       |            | Socket n transmits KeepAlive package:                                              |

|       |            | This command only takes effect when Socket n is in TCP mode.                       |

| 22H   | SEND_KEEP  | Actively transmit a heartbeat packet to the opposite device. If no reply is        |

|       |            | obtained after the timeout, Sn_INT[3] is set to 1, and the value of Sn_STA         |