Overview

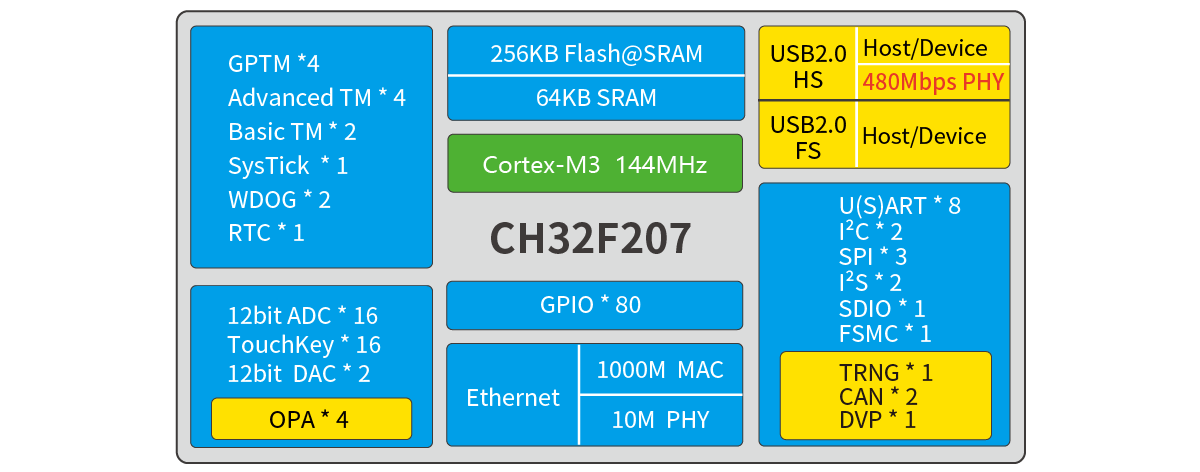

The CH32F205/7 is an industrial-grade interconnectivity MCU based on the Cortex-M3 core. The system clock frequency can be up to 144MHz, and GPIO is supplied independently (separated from the system power supply). Compared with CH32F103, CH32F205/7 has an additional random number unit and 4 operational amplifier comparators. The number of UARTs is increased to 8, and the number of motor timers is increased to 4. CH32F205/7 provides clock security system, power management, dual DMA, DAC, SDIO, CAN, FSMC and other resources. CH32F205/7 also provides USB2.0 high-speed interface (480Mbps) with built-in PHY transceiver, and Ethernet MAC upgraded to Gigabit with integrated 10M PHY module.

System Block Diagram

Features

- Cortex-M3 core, up to 144MHz system clock frequency.

- Single-cycle multiplication and hardware division.

- 64KB SRAM, 256KB Flash.

- Supply voltage: 2.5/3.3V. GPIO unit is supplied independently.

- Low-power modes: sleep, stop, standby.

- Power-on/power-down reset, programmable voltage detector.

- 2 x 18-channel general DMA.

- 4 op amp comparators.

- One true random number generator (TRNG).

- 2 x 12-bit DAC converters.

- 2-unit 16-channel 12-bit ADC converters, 16-channel TouchKey.

- 10 timers.

- USB2.0 full-speed OTG interface.

- USB2.0 high-speed host/device interface (480Mbps, built-in PHY).

- 3 USARTs and 5 UARTs.

- 2 CAN interfaces (2.0B active).

- SDIO interface, FSMC interface, DVP.

- 2 IIC interfaces, 3 SPI interfaces, 2 IIS interfaces.

- Gigabit Ethernet controller ETH (built-in 10M PHY).

- 80 I/O ports, can be mapped to 16 external interrupts.

- CRC calculation unit, 96-bit unique ID.

- Serial 2-wire debug interface.

- Packages: LQFP64M, LQFP100.

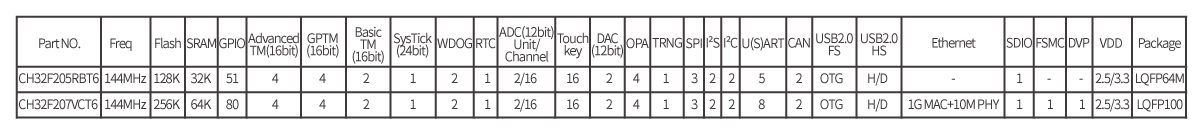

Product Selection Guide

Technical Resources

- Datasheet: CH32F20xDS0.PDF,CH32FV2x_V3xRM.PDF

- CH32F203EVT evaluation board manual and reference routines: CH32F20xEVT.ZIP