QingKeV4_Processor_Manual.PDF

| The scope of application | version | upload time | size | |

|---|---|---|---|---|

| CH32V203F6P6,CH32V203F8P6,CH32V203G6U6,CH32V203G8R6,CH32V203K6T6,CH32V203C6T6,CH32V203K8T6,CH32V203C8T6,CH32V203C8U6,CH32V203RBT6, CH32V303CBT6,CH32V303RBT6,CH32V303RCT6,CH32V303VCT6 CH32V305RBT6,CH32V307RCT6,CH32V307VCT6, CH32V208CBU6,CH32V208RBT6,CH32V208WBU6 | 1.4 | 2025-03-12 | 468KB | |

| QingKe V4 series microprocessor manual,QingKe V4 series microprocessors are self-developed 32-bit general-purpose MCU microprocessors based on the standard RISC-V Instruction Set Architecture (ISA). According to different application scenarios and instruction set combinations, the series includes V4A, V4B, V4C, V4F. V4 series all support RV32IMAC instruction set extensions, among which V4F supports single-precision hardware floating-point, i.e. RV32IMACF extensions. In addition, they also support Hardware Prologue/Epilogue (HPE), Vector Table Free (VTF), a streamlined 2-wire serial debug interface (SDI), support for "WFE" instructions, Physical Memory Protection (PMP), and other features. | ||||

| download | ||||

relation files

| file name | file content |

|---|---|

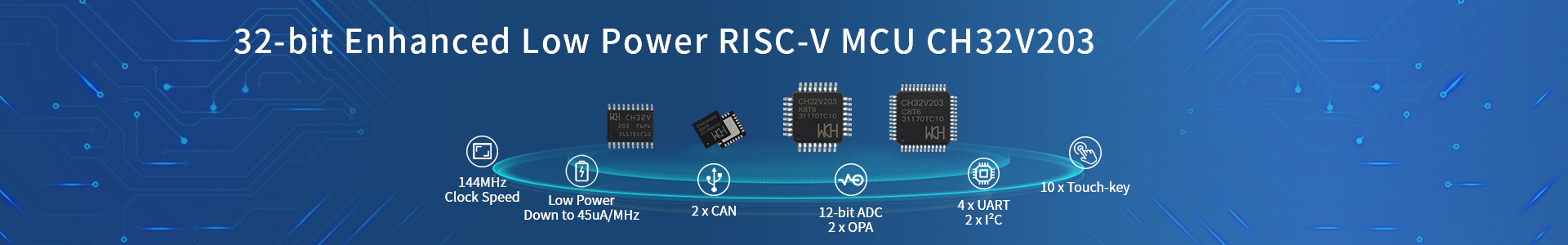

| CH32V203DS0.PDF | CH32V203 is an industrial-grade enhanced low-power, small-medium capacity general-purpose microcontroller designed based on 32-bit RISC-V core, equipped with V4B core, and the operating and sleeping power consumption is significantly reduced year-on-year. It supports USB Host and USB Device functions, etc. |

| CH32V208DS0.PDF | CH32V208 is a wireless microcontroller based on 32-bit RISC-V core, equipped with V4C core, increased memory protection function, and reduced hardware division cycle. It supports 2Mbps low-power Bluetooth BLE communication module, etc. |

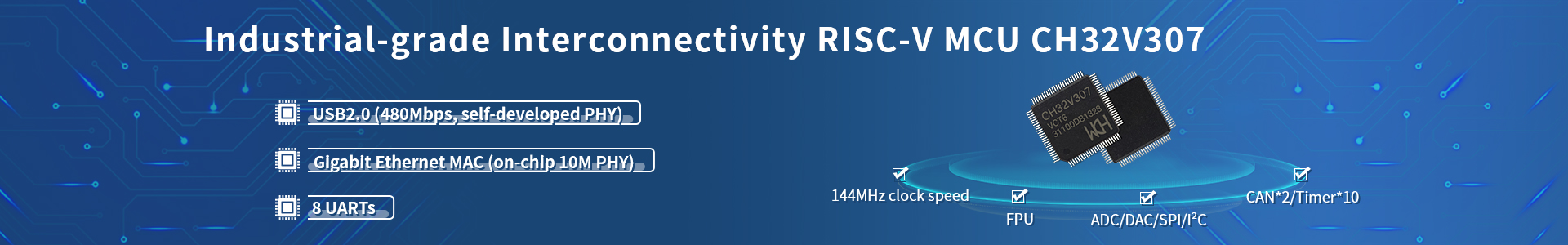

| CH32V307DS0.PDF | CH32V303/305/307/317 datasheet, this series of chips is a high-capacity general-purpose microcontroller designed based on 32-bit RISC-V core, equipped with V4F core, supporting single-precision floating-point instruction set, with higher computing performance. CH32V317 integrates USB2.0 high-speed interface (480Mbps) with built-in PHY transceiver, 100M Ethernet PHY and so on. The CH32V317 integrates USB2.0 high-speed interface (480Mbps) with built-in PHY transceiver, 100M Ethernet PHY, etc. |

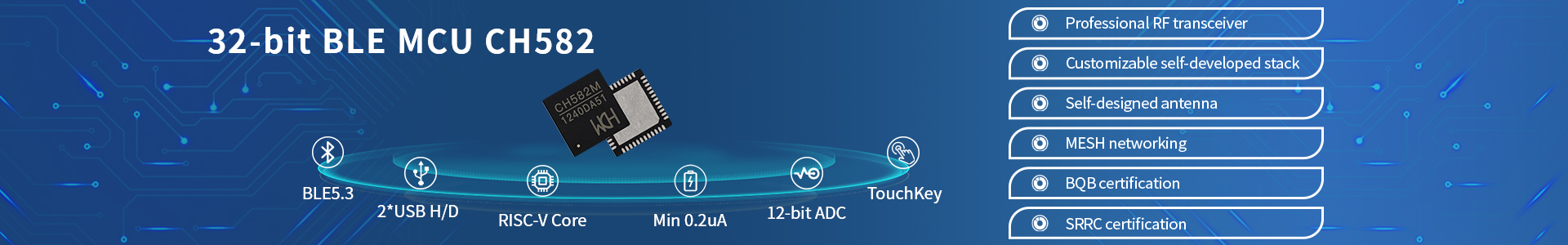

| CH583DS1.PDF | CH583 datasheet. An MCU based on 32-bit RISC-V instruction set integrated with BLE wireless communication. 448K ROM. 32K SRAM. 0.3uA Min current in low-power mode. It integrates 2 independent full-speed USB host/device controllers and transceiver, 12-bit ADC, touch-key detection module, RTC, power management and other peripheral resources. It provides BLE protocol stack and API. |