Overview

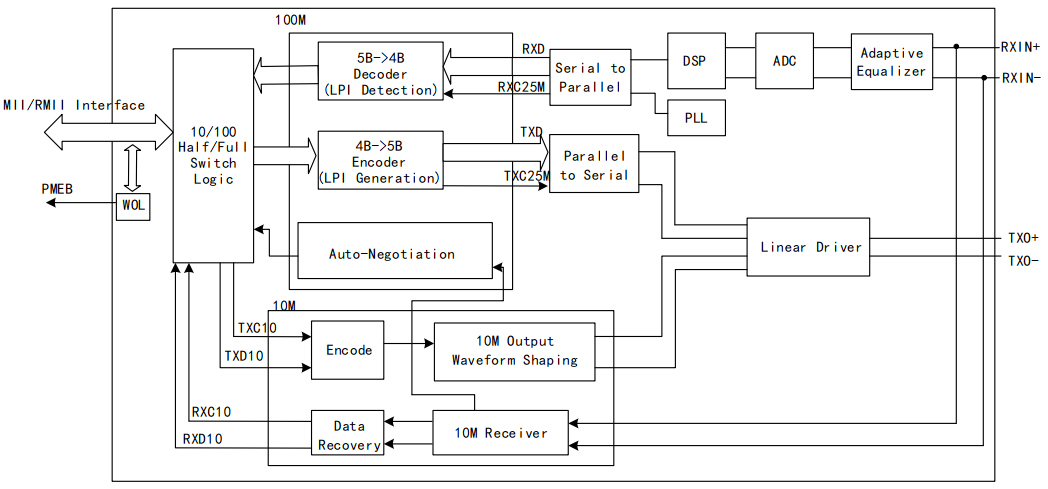

CH182 is an industrial grade 10/100M Ethernet PHY transceiver with Auto-MDIX support. CH182 internally includes Physical Coding Sublayer (PCS), Physical Media Access Layer (PMA), Twisted Pair Physical Medium Dependent (TP-PMD), 10BASE-TX encoder/decoder, Twisted Pair Media Attachment Unit (TPMAU), MII and RMII interfaces, and other modules required for Ethernet Transceiver functions.

The following figure shows the block diagram of CH182.

Features

- Low-power Ethernet physical layer transceiver PHYceiver implemented based on DSP algorithm.

- Support downtime mode.

- Support Auto-MDIX switching TX/RX and automatic identification of positive and negative signal lines.

- Support 10BASE-T and 100BASE-TX and auto-negotiation.

- Support both MII and RMII interface modes.

- Support full-duplex and half-duplex operation.

- Support UTP CAT5E and CAT6 twisted pair cable, support 120m transmission distance.

- Built-in LDO, supports independent I/O interface power supply for different voltage processors or MCUs.

- Built-in 50Ω impedance matching resistor, built-in capacitor required for 25MHz crystal oscillator, and streamlined peripheral circuitry.

- Optional support for external 50MHz clock input.

- Support WOL network wake-up.

- Support interrupt function.

- Support two types of network status LEDs.

- Available in QFN24 and QFN32 packages.

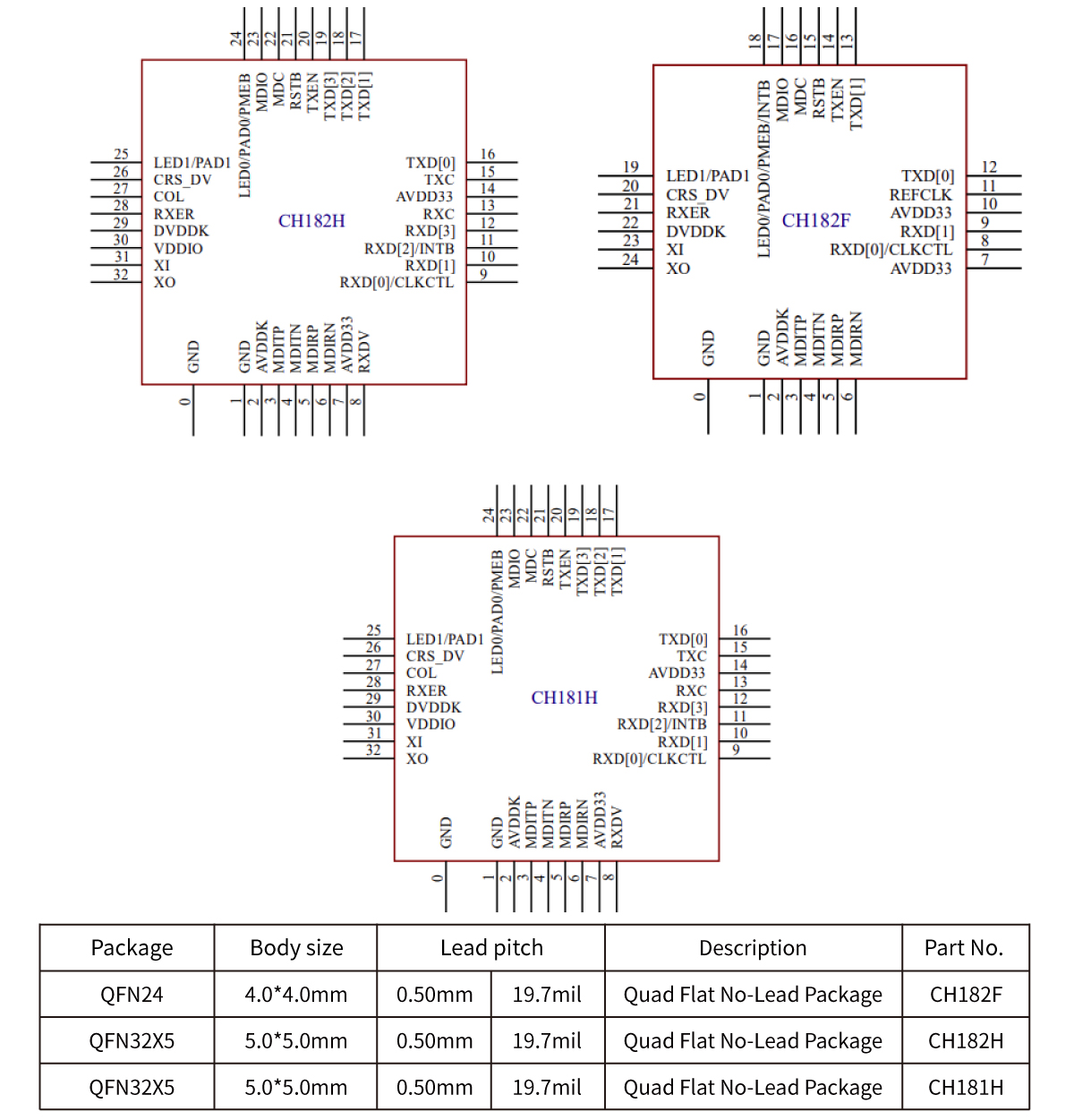

Package

Note: CH182F only supports RMII interface mode.

All other CH182 contents are applicable to CH181 except where specifically marked.

Note: CH182F only supports RMII interface mode.

All other CH182 contents are applicable to CH181 except where specifically marked.