Overview

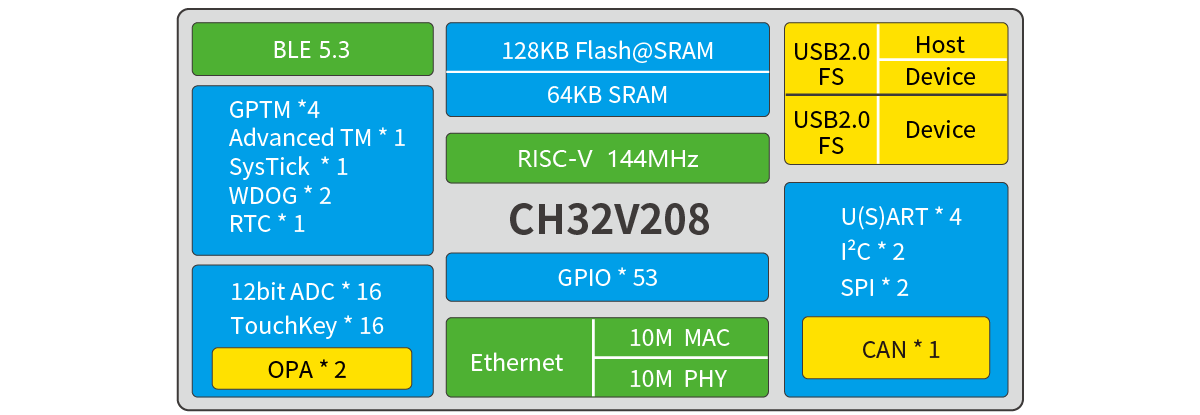

The CH32V208 is a wireless MCU based on 32-bit RISC-V core, with hardware stack area and fast interrupt entry. Compared with standard RISC-V, the interrupt response speed is greatly improved. The CH32V208 is based on V4C core. The memory protection unit is added and hardware division cycle is reduced. The CH32V208 integrates 2Mbps BLE communication module, 10M Ethernet module (MAC+PHY), USB2.0 full-speed device and host/device interface, CAN controller, etc.

System Block Diagram

Features

- Qingke V4C processor, up to 144MHz system clock frequency.

- Single-cycle multiplication and hardware division.

- 64KB SRAM, 128KB Flash.

- Supply voltage: 2.5V/3.3V. GPIO unit is supplied independently.

- Low-power modes: sleep/stop/standby.

- Bluetooth Low Energy 5.3.

- 10M Ethernet controller (MAC+PHY).

- Power-on/power-down reset (POR/PDR), programmable voltage detector (PVD).

- 2 amplifiers.

- 16-channel 12-bit ADC, 16-channel TouchKey.

- 5 timers.

- USB2.0 full-speed host/device + device interface.

- 4 USARTs.

- One CAN interface (2.0B active).

- 2 IIC interfaces, 2 SPI interfaces.

- 53 I/O ports, can be mapped to 16 external interrupts.

- CRC calculation unit, 96-bit unique ID.

- Serial 2-wire debug interface.

- Packages: LQFP64M, QFN68, QFN48, QFN28.

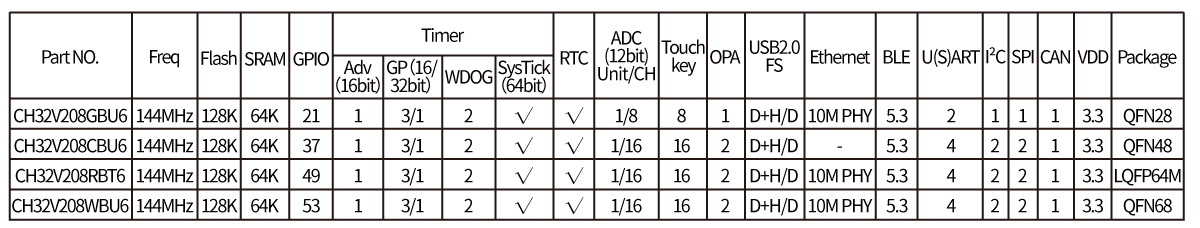

Product Selection Guide

Technical Resources

- Datasheet: CH32V20x_30xDS0.PDF,CH32FV2x_V3xRM.PDF

- Integrated development environment (IDE): MounRiver Studio(MRS)