Introduction

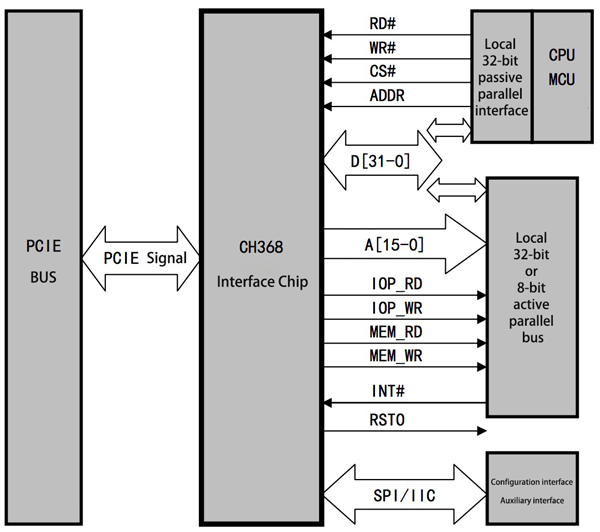

CH368 is a universal interface chip that connects to PCI-Express bus, supports I/O port mapping, memory mapping, extended ROM and interrupts. CH368 converts high-speed PCIE bus into an easy-to-use 32-bit or 8-bit active parallel interface which similar to ISA bus. It can be used for making low-cost PCIE bus-based computer cards, and upgrade to PCIE card from ISA or PCI bus based. Compared with other bus, PCIE is faster, real-time, better on control, so CH368 is suitable for high-speed real-time I/O control card, communication interface card, data acquisition card and so on.

The figure below shows is application block diagram.

Features

- Provides 8-bit or 32-bit active parallel bus based on PCIE bus.

- Provides 32-bit passive parallel interface, can be connected to other CPU or MCU bus, supports BusMaster/ DMA.

- Supports I/O read and write, automatic allocation of I/O base, supports up to 232 bytes of I/O port.

- Supports memory read and write, supports memory prefetch, direct mapping supports memory SRAM which capacity is 32KB.

- Read and write pulse width from 30nS to 450nS optional, 32-bit memory burst block access speed up to 50MB per second.

- Supports request input of level interrupt or edge interrupt, supports interrupt sharing.

- Supports flash expansion ROM boot without hard disk, provide extended ROM application subroutine library BRM.

- Provides high-speed 3-wire or 4-wire SPI serial host interface.

- Provides two-wire serial master interface, can hang serial EEPROM similar with 24C0X to store non-volatile data.

- Supports that can be set for device ID (Vendor ID, Device ID, Class Code, etc.) of PCI board in EEPROM.

- Built-in 2uS to 8mS hardware timing unit as delay reference for software operation.

- Driver supports Windows 98/Me/2000/XP/Vista/7/8/8.1/10/SERVER 2003/2008/2012/2016 and Linux, provide application API through the DLL.

- 3.3V supply voltage, I/O pin supports 5V withstand voltage, supports low power sleep mode.

- LQFP-100 lead-free package, RoHS compliant.