Overview

CH394 is an Ethernet protocol stack management chip, which is used for Ethernet communication in MCU system.

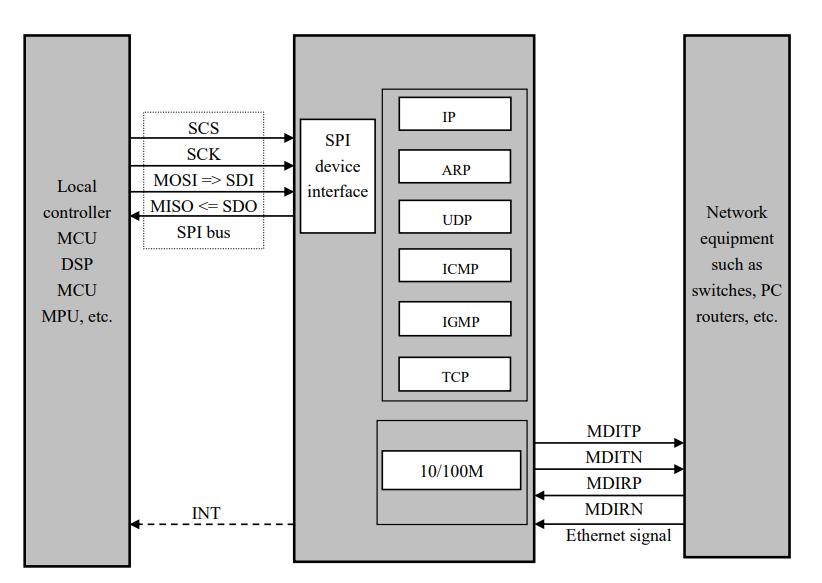

CH394 chip comes with 10/100M Ethernet Media Access Control (MAC) and Physical layer (PHY), which is fully compatible with IEEE802.3 protocol, and has built-in Ethernet protocol stack firmware such as IP, ARP, ICMP, IGMP, UDP and TCP. MCU system can conveniently communicate with the network through CH394 chip. CH394 supports Wake-on-LAN (WOL) and power-down mode.

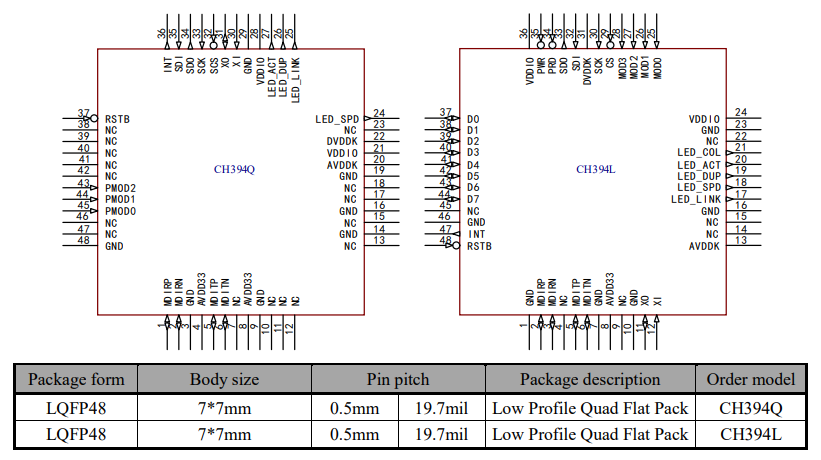

CH394Q provides SPI interface, CH394L provides SPI interface and 8-bit slave parallel interface. Controllers such as MCU/DSP/MPU can control CH394Q chip to communicate with Ethernet through SPI interface. Or through SPI interface or 8-bit parallel port to control CH394L chip for Ethernet communication.

The following figure shows the application block diagram of CH394Q.

Features

- Built-in Ethernet Media Access Control (MAC) and Physical layer (PHY)

- Support 10/100M, full-duplex/half-duplex adaptation, and is compatible with 802.3 protocol

- Support automatic conversion of MDI/MDIX lines

- Built-in TCP/IP protocol suite. Support IPv4, ARP, ICMP, IGMP, UDP and TCP protocols

- CH394Q supports 8 sockets and CH394L supports 4 sockets. Can transmit and receive data at the same time

- Support MAC RAW mode and IP RAW mode (IP RAW mode is only supported by CH394L)

- Provide a SPI slave interface (SPI mode 0 or 3) up to 40MHz, with the high bit coming first

- The CH394L provides a high-speed 8-bit slave parallel interface that supports a parallel data bus connected to the microcontroller.

- Support network Wake-on-LAN (WOL) and power-down mode

- LED status display (Link, ACT, 10/100M, full-duplex/half-duplex, etc.)

- Built-in 32KRAM can be used for Ethernet data transceiver, and each Socket transceiver buffer can be configured flexibly

- LQFP48 lead-free package

Package